# Spartan-3 Generation Configuration User Guide

Spartan™-3A, Spartan-3AN, Spartan-3A DSP, Spartan-3E, and Spartan-3 FPGA Families

UG332 (v1.3) November 21, 2007

Xilinx is disclosing this Document and Intellectual Property (hereinafter "the Design") to you for use in the development of designs to operate on, or interface with Xilinx FPGAs. Except as stated herein, none of the Design may be copied, reproduced, distributed, republished, downloaded, displayed, posted, or transmitted in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Any unauthorized use of the Design may violate copyright laws, trademark laws, the laws of privacy and publicity, and communications regulations and statutes.

Xilinx does not assume any liability arising out of the application or use of the Design; nor does Xilinx convey any license under its patents, copyrights, or any rights of others. You are responsible for obtaining any rights you may require for your use or implementation of the Design. Xilinx reserves the right to make changes, at any time, to the Design as deemed desirable in the sole discretion of Xilinx. Xilinx assumes no obligation to correct any errors contained herein or to advise you of any correction if such be made. Xilinx will not assume any liability for the accuracy or correctness of any engineering or technical support or assistance provided to you in connection with the Design.

THE DESIGN IS PROVIDED "AS IS" WITH ALL FAULTS, AND THE ENTIRE RISK AS TO ITS FUNCTION AND IMPLEMENTATION IS WITH YOU. YOU ACKNOWLEDGE AND AGREE THAT YOU HAVE NOT RELIED ON ANY ORAL OR WRITTEN INFORMATION OR ADVICE, WHETHER GIVEN BY XILINX, OR ITS AGENTS OR EMPLOYEES. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DESIGN, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND NONINFRINGEMENT OF THIRD-PARTY RIGHTS.

IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOST DATA AND LOST PROFITS, ARISING FROM OR RELATING TO YOUR USE OF THE DESIGN, EVEN IF YOU HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. THE TOTAL CUMULATIVE LIABILITY OF XILINX IN CONNECTION WITH YOUR USE OF THE DESIGN, WHETHER IN CONTRACT OR TORT OR OTHERWISE, WILL IN NO EVENT EXCEED THE AMOUNT OF FEES PAID BY YOU TO XILINX HEREUNDER FOR USE OF THE DESIGN. YOU ACKNOWLEDGE THAT THE FEES, IF ANY, REFLECT THE ALLOCATION OF RISK SET FORTH IN THIS AGREEMENT AND THAT XILINX WOULD NOT MAKE AVAILABLE THE DESIGN TO YOU WITHOUT THESE LIMITATIONS OF LIABILITY.

The Design is not designed or intended for use in the development of on-line control equipment in hazardous environments requiring failsafe controls, such as in the operation of nuclear facilities, aircraft navigation or communications systems, air traffic control, life support, or weapons systems ("High-Risk Applications"). Xilinx specifically disclaims any express or implied warranties of fitness for such High-Risk Applications. You represent that use of the Design in such High-Risk Applications is fully at your risk.

© 2006-2007 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

#### **Revision History**

The following table shows the revision history for this document.

| Date     | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12/05/06 | 1.0     | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 02/26/07 | 1.1     | Added configuration information for the <u>Spartan-3AN FPGA</u> family. Added <u>Chapter 10</u> , "Internal Master SPI Mode" describing how a Spartan-3AN FPGA configures from its internal In-System Flash memory. Increased <u>ConfigRate</u> settings for Spartan-3A/3AN FPGAs based on improved data setup time ( <u>Table 4-11</u> and <u>Table 5-8</u> ). Added links to new reference designs using the <u>Spartan-3E</u> and <u>Spartan-3A</u> Starter Kit boards. |

| 05/23/07 | 1.2     | Added Spartan-3A DSP family configuration information. Added "Bitstream Format," page 26. Added "Indirect SPI Programming using iMPACT," page 120. Updated "Limitations when Reprogramming via JTAG if FPGA Set for BPI Configuration," page 160. Updated JTAG ID values in Table 12-4, page 236. Added more information to "Configuration Watchdog Timer (CWDT) and Fallback," page 274.                                                                                  |

| Date     | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

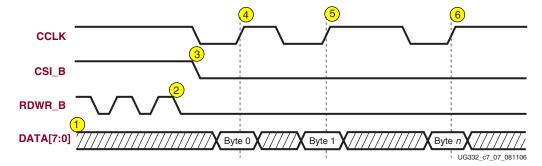

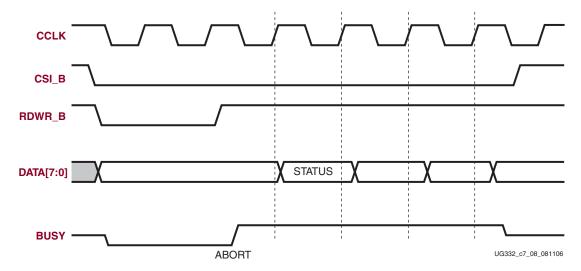

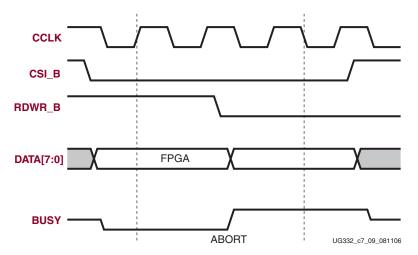

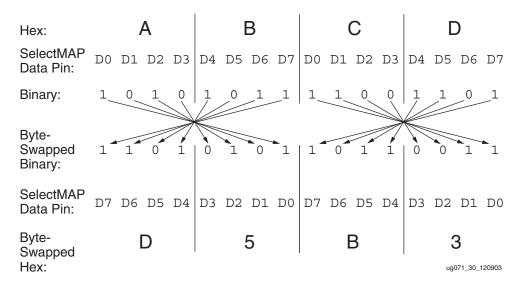

| 11/21/07 | 1.3     | Noted in "Non-Continuous SelectMAP Data Loading" that "Deasserting CSI_B" is not supported in the Spartan-3A, Spartan-3AN, and Spartan-3A DSP FPGA families. Added "Indirect Parallel Flash Programming Using iMPACT". Updated Figure 5-14 to showD[7:0] inputs clocked on rising CCLK edge. Added "Byte Swapping" description. Added JTAG TAP Controller State descriptions in Table 9-2. Updated Spartan-3AN FPGA Variant Select options in Table 10-2. Updated Figure 14-20 and description to note that MultiBoot Variant Select is based on Read Command from GENERAL2 register when NEWMODE=1, not BOOTVSEL bits in MODE_REG. Updated software version references throughout. Updated documentation links throughout. |

## Table of Contents

| Design Considerations   13     Will the FPGA be used in a PCIP* application?   25     Where to go for debugging support   25     FPGA Configuration Bitstream Sizes   26     Uncompressed Bitstream Image Size   26     Bitstream Format   26     Synchronization Word   27     Array ID   27     Data Frames   27     CRC   28     Bitstream Compression   28     Packet Format   29     Setting Bitstream Options, Generating an FPGA Bitstream   29     Setting Bitstream Options, Generating an FPGA Bitstream   29     SE Software Project Navigator   30     BitGen Command Line Utility   34     Chapter 2: Configuration Pins and Behavior during Configuration General Configuration Mode: M[2:0]   36     M[2:0] Functional Differences between Spartan-3 Generation Families   36     Spartan-3 A/3AN/3A DSP and Spartan-3E FPGA Families   37     Spartan-3 FPGA Family   37     Defining M[2:0] after Configuration for Minimum Power Consumption   37     DONE Pin   38     Associated Bitstream Generator (BitGen) Options   38     DONE Synchronizes Multiple FPGAs in a Daisy Chain Configuration   40     Program or Reset FPGA: PROG_B   41     Configuration Clock: CCLK   42     CCLK Differences between Spartan-3 Generation FPGA Families   42     CLK Design Considerations   44     Configuration Clock: CCLK   46     Persist: Reserve CCLK As Part of SelectMAP Interface   46     Spartan-3A/3AN/3A DSP PaGA Post-Configuration Error: INIT_B   47     After Configuration Memory, Configuration Error: INIT_B   47     After Configuration Pins   48     Spartan-3A/3AN/3A DSP PaGA Post-Configuration CRC   48     Spartan-3A/3AN/  | Chapter 1: Overview and Design Considerations            |          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------|

| Will the FPGA be used in a PCI™ application?   25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Design Considerations                                    | 13       |

| FPGA Configuration Bitstream Sizes         26           Uncompressed Bitstream Image Size         26           Bitstream Format         26           Synchronization Word         27           Array ID         27           Data Frames         27           CRC         28           Bitstream Compression         28           Packet Format         29           Setting Bitstream Options, Generating an FPGA Bitstream         29           ISE Software Project Navigator         30           BitGen Command Line Utility         34           Chapter 2: Configuration Pins and Behavior during Configuration         36           General Configuration Control Pins         35           Choose a Configuration Mode: M[2:0]         36           M[2:0] Functional Differences between Spartan-3 Generation Families         36           Spartan-3 FPGA Family         36           Spartan-3 FPGA Family         37           Defining M[2:0] after Configuration for Minimum Power Consumption         37           DONE Pin         38           Associated Bitstream Generator (BitGen) Options         38           DONE Synchronizes Multiple FPGAs in a Daisy Chain Configuration         40           Program or Reset FPGA: PROG B         41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                          |          |

| Uncompressed Bitstream Image Size 26 Bitstream Format 26 Synchronization Word 27 Array ID 27 Data Frames 27 CRC. 27 CRC. 28 Bitstream Compression 28 Packet Format 29 Setting Bitstream Options, Generating an FPGA Bitstream 29 ISE Software Project Navigator 30 BitGen Command Line Utility 34  Chapter 2: Configuration Pins and Behavior during Configuration General Configuration Control Pins 35 Choose a Configuration Mode: M[2:0] 36 M[2:0] Functional Differences between Spartan-3 Generation Families 36 Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families 37 Spartan-3 FPGA Family 37 Defining M[2:0] after Configuration for Minimum Power Consumption 37 DONE Pin 38 Associated Bitstream Generator (BitGen) Options 38 DONE Synchronizes Multiple FPGAs in a Daisy Chain Configuration 40 Program or Reset FPGA: PROG_B 41 Configuration Clock: CCLK 42 CCLK Differences between Spartan-3 Generation FPGA Families 42 CCLK Design Considerations 42 CCLK Design Considerations 44 Configuration Clock: CCLK 48 Persist: Reserve CCLK As Part of SelectMAP Interface 46 Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families 47 Spartan-3 FPGA Family 47 Initializing Configuration Memory, Configuration Error: INIT_B 47 After Configuration Memory, Configuration Error: INIT_B 48 Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families 48 Spartan-34 PGA Family 48 Pins with Optional Pull-Up Resistors during Configuration 50 P | Where to go for debugging support                        | 25       |

| Uncompressed Bitstream Image Size 26 Bitstream Format 26 Synchronization Word 27 Array ID 27 Data Frames 27 CRC. 27 CRC. 28 Bitstream Compression 28 Packet Format 29 Setting Bitstream Options, Generating an FPGA Bitstream 29 ISE Software Project Navigator 30 BitGen Command Line Utility 34  Chapter 2: Configuration Pins and Behavior during Configuration General Configuration Control Pins 35 Choose a Configuration Mode: M[2:0] 36 M[2:0] Functional Differences between Spartan-3 Generation Families 36 Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families 37 Spartan-3 FPGA Family 37 Defining M[2:0] after Configuration for Minimum Power Consumption 37 DONE Pin 38 Associated Bitstream Generator (BitGen) Options 38 DONE Synchronizes Multiple FPGAs in a Daisy Chain Configuration 40 Program or Reset FPGA: PROG_B 41 Configuration Clock: CCLK 42 CCLK Differences between Spartan-3 Generation FPGA Families 42 CCLK Design Considerations 42 CCLK Design Considerations 44 Configuration Clock: CCLK 48 Persist: Reserve CCLK As Part of SelectMAP Interface 46 Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families 47 Spartan-3 FPGA Family 47 Initializing Configuration Memory, Configuration Error: INIT_B 47 After Configuration Memory, Configuration Error: INIT_B 48 Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families 48 Spartan-34 PGA Family 48 Pins with Optional Pull-Up Resistors during Configuration 50 P | FPGA Configuration Bitstream Sizes                       | 26       |

| Bitstream Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                          |          |

| Array ID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                          |          |

| Data Frames                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Synchronization Word                                     | 27       |

| CRC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                          |          |

| Bitstream Compression 28 Packet Format 29 Setting Bitstream Options, Generating an FPGA Bitstream 29 ISE Software Project Navigator 30 BitGen Command Line Utility 34  Chapter 2: Configuration Pins and Behavior during Configuratior General Configuration Control Pins 35 Choose a Configuration Mode: M[2:0] 36 M[2:0] 36 M[2:0] Functional Differences between Spartan-3 Generation Families 36 Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families 37 Spartan-3 FPGA Family 37 DoNie Pin 38 Associated Bitstream Generator (BitGen) Options 38 DONE Synchronizes Multiple FPGAs in a Daisy Chain Configuration 40 Program or Reset FPGA: PROG_B 41 Configuration Clock: CCLK 42 CCLK Differences between Spartan-3 Generation FPGA Families 42 CCLK Design Considerations 42 CCLK Design Considerations 44 Configuration Clock: CCLK 46 Persist: Reserve CCLK As Part of SelectMAP Interface 46 Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families 47 Spartan-3 FPGA Family 47 Initializing Configuration Memory, Configuration Error: INIT_B 47 After Configuration Memory, Configuration Error: INIT_B 48 Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families 48 Spartan-3B FPGA Family 48 Pull-Up Resistors During Configuration Error: INIT_B 59 Pins with Dedicated Pull-Up Resistors during Configuration 50 FPGA Pull-Up Resistors Values 50 Pin Description 50                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                          |          |

| Packet Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                          |          |

| Setting Bitstream Options, Generating an FPGA Bitstream                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | *                                                        |          |

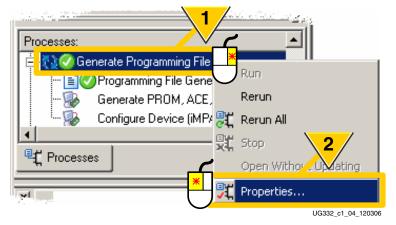

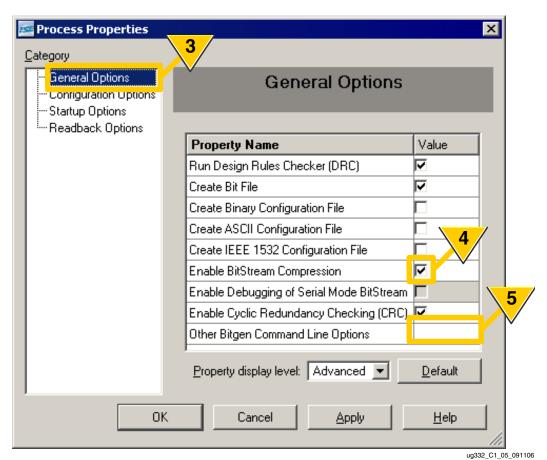

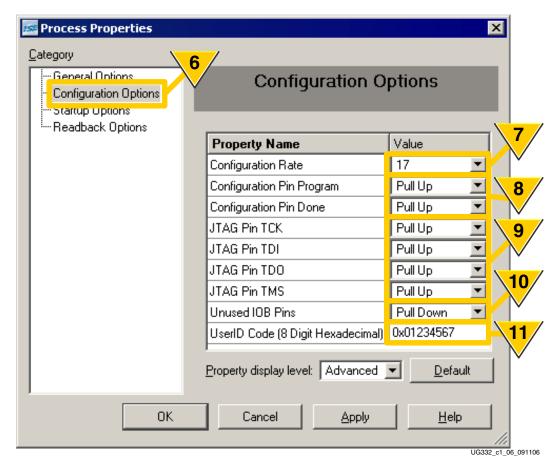

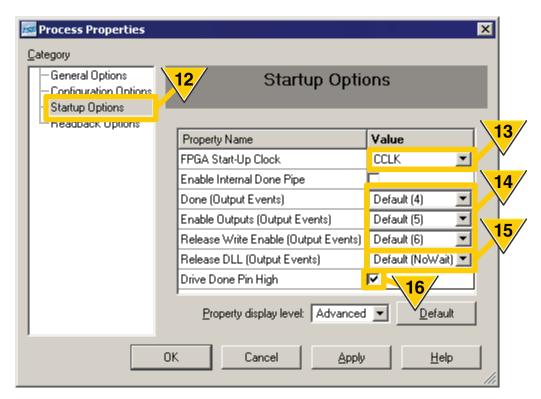

| ISE Software Project Navigator BitGen Command Line Utility  34  Chapter 2: Configuration Pins and Behavior during Configuration General Configuration Mode: M[2:0]  35  Choose a Configuration Mode: M[2:0]  36  M[2:0] Functional Differences between Spartan-3 Generation Families  36  Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families  37  Spartan-3 FPGA Family  37  Defining M[2:0] after Configuration for Minimum Power Consumption  37  DONE Pin  38  Associated Bitstream Generator (BitGen) Options  38  DONE Synchronizes Multiple FPGAs in a Daisy Chain Configuration  40  Program or Reset FPGA: PROG_B  41  Configuration Clock: CCLK  22  CCLK Differences between Spartan-3 Generation FPGA Families  42  CCLK Design Considerations  44  ConfigRate: Bitstream Option for CCLK.  46  Persist: Reserve CCLK As Part of SelectMAP Interface  46  Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families  47  Spartan-3 FPGA Family  47  Initializing Configuration Memory, Configuration Error: INIT_B  47  After Configuration  47  Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families  48  Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families  49  Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families  47  Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families  48  Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families  49  Pins with Optional Pull-Up Resistors during Configuration  48  Pins with Optional Pull-Up Resistors during Configuration  50  FPGA Pull-Up Resistor Values  50  Pin Description  52                                                                                                                                                                                                                                              |                                                          |          |

| BitGen Command Line Utility         34           Chapter 2: Configuration Pins and Behavior during Configuration           General Configuration Control Pins         35           Choose a Configuration Mode: M[2:0]         36           M[2:0] Functional Differences between Spartan-3 Generation Families         36           Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families         37           Spartan-3 FPGA Family         37           Defining M[2:0] after Configuration for Minimum Power Consumption         37           DONE Pin         38           Associated Bitstream Generator (BitGen) Options         38           DONE Synchronizes Multiple FPGAs in a Daisy Chain Configuration         40           Program or Reset FPGA: PROG_B         41           Configuration Clock: CCLK         42           CCLK Differences between Spartan-3 Generation FPGA Families         42           CCLK Design Considerations         44           ConfigRate: Bitstream Option for CCLK.         46           Persist: Reserve CCLK As Part of SelectMAP Interface         46           Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families         47           Spartan-3PGA Family         47           Initializing Configuration Memory, Configuration Error: INIT_B         47           Spartan-3A/3AN/3A DSP and S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                          |          |

| Chapter 2: Configuration Pins and Behavior during Configuration  General Configuration Control Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                          |          |

| General Configuration Control Pins35Choose a Configuration Mode: M[2:0]36M[2:0] Functional Differences between Spartan-3 Generation Families36Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families37Spartan-3 FPGA Family37Defining M[2:0] after Configuration for Minimum Power Consumption37DONE Pin38Associated Bitstream Generator (BitGen) Options38DONE Synchronizes Multiple FPGAs in a Daisy Chain Configuration40Program or Reset FPGA: PROG_B41Configuration Clock: CCLK42CCLK Differences between Spartan-3 Generation FPGA Families42CCLK Design Considerations44ConfigRate: Bitstream Option for CCLK.46Persist: Reserve CCLK As Part of SelectMAP Interface46Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families47Initializing Configuration Memory, Configuration Error: INIT_B47After Configuration47Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families48Spartan-3 FPGA Family48Partan-3 FPGA Family48Partan-3 FPGA Family48Pull-Up Resistors During Configuration48Pins with Optional Pull-Up Resistors during Configuration48Pins with Optional Pull-Up Resistors during Configuration50FPGA Pull-Up Resistor Values50Pin Description52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | BitGen Command Line Utility                              | 34       |

| General Configuration Control Pins35Choose a Configuration Mode: M[2:0]36M[2:0] Functional Differences between Spartan-3 Generation Families36Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families37Spartan-3 FPGA Family37Defining M[2:0] after Configuration for Minimum Power Consumption37DONE Pin38Associated Bitstream Generator (BitGen) Options38DONE Synchronizes Multiple FPGAs in a Daisy Chain Configuration40Program or Reset FPGA: PROG_B41Configuration Clock: CCLK42CCLK Differences between Spartan-3 Generation FPGA Families42CCLK Design Considerations44ConfigRate: Bitstream Option for CCLK.46Persist: Reserve CCLK As Part of SelectMAP Interface46Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families47Initializing Configuration Memory, Configuration Error: INIT_B47After Configuration47Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families48Spartan-3 FPGA Family48Partan-3 FPGA Family48Partan-3 FPGA Family48Pull-Up Resistors During Configuration48Pins with Optional Pull-Up Resistors during Configuration48Pins with Optional Pull-Up Resistors during Configuration50FPGA Pull-Up Resistor Values50Pin Description52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                          |          |

| Choose a Configuration Mode: M[2:0] 36 M[2:0] Functional Differences between Spartan-3 Generation Families 36 Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families 37 Spartan-3 FPGA Family 37 Defining M[2:0] after Configuration for Minimum Power Consumption 37 DONE Pin 38 Associated Bitstream Generator (BitGen) Options 38 DONE Synchronizes Multiple FPGAs in a Daisy Chain Configuration 40 Program or Reset FPGA: PROG_B 41 Configuration Clock: CCLK 42 CCLK Differences between Spartan-3 Generation FPGA Families 42 CCLK Design Considerations 44 ConfigRate: Bitstream Option for CCLK. 46 Persist: Reserve CCLK As Part of SelectMAP Interface 46 Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families 47 Spartan-3 FPGA Family 47 Initializing Configuration Memory, Configuration Error: INIT_B 47 After Configuration Memory, Configuration Error: INIT_B 47 Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families 48 Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families 48 Spartan-3 FPGA Family 48 Pull-Up Resistors During Configuration A8 Pins with Dedicated Pull-Up Resistors during Configuration 48 Pins with Optional Pull-Up Resistors during Configuration 50 FPGA Pull-Up Resistor Values 50  Pin Description 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Chapter 2: Configuration Pins and Benavior during Config | juration |

| M[2:0] Functional Differences between Spartan-3 Generation Families 36 Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families 37 Spartan-3 FPGA Family 37 Defining M[2:0] after Configuration for Minimum Power Consumption 37 DONE Pin 38 Associated Bitstream Generator (BitGen) Options 38 DONE Synchronizes Multiple FPGAs in a Daisy Chain Configuration 40 Program or Reset FPGA: PROG_B 41 Configuration Clock: CCLK 42 CCLK Differences between Spartan-3 Generation FPGA Families 42 CCLK Design Considerations 44 ConfigRate: Bitstream Option for CCLK. 46 Persist: Reserve CCLK As Part of SelectMAP Interface 46 Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families 47 Spartan-3 FPGA Family 47 Initializing Configuration Memory, Configuration Error: INIT_B. 47 After Configuration SPF FPGA Post-Configuration CRC 48 Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families 48 Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families 48 Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families 48 Spartan-3A/3AN/3A DSP profiguration CRC 48 Spartan-3A/3AN/3A DSP profiguration CRC 48 Spartan-3FPGA Family 48 Pull-Up Resistors During Configuration 48 Pins with Dedicated Pull-Up Resistors during Configuration 48 Pins with Optional Pull-Up Resistors during Configuration 50 FPGA Pull-Up Resistor Values 50  Pin Description 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | General Configuration Control Pins                       | 35       |

| Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families37Spartan-3 FPGA Family37Defining M[2:0] after Configuration for Minimum Power Consumption37DONE Pin38Associated Bitstream Generator (BitGen) Options38DONE Synchronizes Multiple FPGAs in a Daisy Chain Configuration40Program or Reset FPGA: PROG_B41Configuration Clock: CCLK42CCLK Differences between Spartan-3 Generation FPGA Families42CCLK Design Considerations44ConfigRate: Bitstream Option for CCLK46Persist: Reserve CCLK As Part of SelectMAP Interface46Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families47Spartan-3 FPGA Family47Initializing Configuration Memory, Configuration Error: INIT_B47After Configuration47Spartan-3A/3AN/3A DSP FPGA Post-Configuration CRC48Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families48Spartan-3 FPGA Family48Pull-Up Resistors During Configuration48Pins with Dedicated Pull-Up Resistors during Configuration48Pins with Optional Pull-Up Resistors during Configuration50FPGA Pull-Up Resistor Values50Pin Description52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                          |          |

| Spartan-3 FPGA Family Defining M[2:0] after Configuration for Minimum Power Consumption. 37 DONE Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          |          |

| Defining M[2:0] after Configuration for Minimum Power Consumption. 37 DONE Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                          |          |

| DONE Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                        |          |

| Associated Bitstream Generator (BitGen) Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                          |          |

| DONE Synchronizes Multiple FPGAs in a Daisy Chain Configuration. 40 Program or Reset FPGA: PROG_B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                          |          |

| Program or Reset FPGA: PROG_B Configuration Clock: CCLK CCLK Differences between Spartan-3 Generation FPGA Families CCLK Design Considerations 42 CCLK Design Considerations 44 ConfigRate: Bitstream Option for CCLK 46 Persist: Reserve CCLK As Part of SelectMAP Interface 46 Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families 47 Spartan-3 FPGA Family 47 Initializing Configuration Memory, Configuration Error: INIT_B 47 After Configuration 47 Spartan-3A/3AN/3A DSP FPGA Post-Configuration CRC 48 Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families 48 Spartan-3 FPGA Family 48 Pull-Up Resistors During Configuration 49 Pins with Dedicated Pull-Up Resistors during Configuration 49 Pins with Optional Pull-Up Resistors during Configuration 50 FPGA Pull-Up Resistor Values 50 Pin Description 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          |          |

| Configuration Clock: CCLK  CCLK Differences between Spartan-3 Generation FPGA Families  42 CCLK Design Considerations  44 ConfigRate: Bitstream Option for CCLK.  46 Persist: Reserve CCLK As Part of SelectMAP Interface  46 Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families  47 Spartan-3 FPGA Family  47 Initializing Configuration Memory, Configuration Error: INIT_B  47 After Configuration  47 Spartan-3A/3AN/3A DSP FPGA Post-Configuration CRC  48 Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families  48 Spartan-3 FPGA Family  48 Pull-Up Resistors During Configuration  48 Pins with Dedicated Pull-Up Resistors during Configuration  50 FPGA Pull-Up Resistor Values  50  Pin Description  52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                          |          |

| CCLK Differences between Spartan-3 Generation FPGA Families                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                          |          |

| CCLK Design Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                          |          |

| ConfigRate: Bitstream Option for CCLK. 46 Persist: Reserve CCLK As Part of SelectMAP Interface 46 Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families 47 Spartan-3 FPGA Family 47 Initializing Configuration Memory, Configuration Error: INIT_B 47 After Configuration 59 Spartan-3A/3AN/3A DSP FPGA Post-Configuration CRC 48 Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families 48 Spartan-3 FPGA Family 48 Pull-Up Resistors During Configuration 50 Pins with Optional Pull-Up Resistors during Configuration 50 FPGA Pull-Up Resistor Values 50  Pin Description 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                          |          |

| Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families47Spartan-3 FPGA Family47Initializing Configuration Memory, Configuration Error: INIT_B47After Configuration47Spartan-3A/3AN/3A DSP FPGA Post-Configuration CRC48Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families48Spartan-3 FPGA Family48Pull-Up Resistors During Configuration48Pins with Dedicated Pull-Up Resistors during Configuration48Pins with Optional Pull-Up Resistors during Configuration50FPGA Pull-Up Resistor Values50Pin Description52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                          |          |

| Spartan-3 FPGA Family                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Persist: Reserve CCLK As Part of SelectMAP Interface     | 46       |

| Initializing Configuration Memory, Configuration Error: INIT_B. 47 After Configuration 47 Spartan-3A/3AN/3A DSP FPGA Post-Configuration CRC 48 Spartan-3A/3AN/3A DSP and Spartan-3E FPGA Families 48 Spartan-3 FPGA Family 48 Pull-Up Resistors During Configuration 48 Pins with Dedicated Pull-Up Resistors during Configuration 48 Pins with Optional Pull-Up Resistors during Configuration 50 FPGA Pull-Up Resistor Values 50  Pin Description 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <u>.</u>                                                 |          |