# Spartan-3 Generation FPGA User Guide

# Spartan-3A DSP, Spartan-3AN, Spartan-3A, Spartan-3E, and Spartan-3 FPGA Platforms

UG331 (v1.2) April 2, 2007

Xilinx is disclosing this Document and Intellectual Property (hereinafter "the Design") to you for use in the development of designs to operate on, or interface with Xilinx FPGAs. Except as stated herein, none of the Design may be copied, reproduced, distributed, republished, downloaded, displayed, posted, or transmitted in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Any unauthorized use of the Design may violate copyright laws, trademark laws, the laws of privacy and publicity, and communications regulations and statutes.

Xilinx does not assume any liability arising out of the application or use of the Design; nor does Xilinx convey any license under its patents, copyrights, or any rights of others. You are responsible for obtaining any rights you may require for your use or implementation of the Design. Xilinx reserves the right to make changes, at any time, to the Design as deemed desirable in the sole discretion of Xilinx. Xilinx assumes no obligation to correct any errors contained herein or to advise you of any correction if such be made. Xilinx will not assume any liability for the accuracy or correctness of any engineering or technical support or assistance provided to you in connection with the Design.

THE DESIGN IS PROVIDED "AS IS" WITH ALL FAULTS, AND THE ENTIRE RISK AS TO ITS FUNCTION AND IMPLEMENTATION IS WITH YOU. YOU ACKNOWLEDGE AND AGREE THAT YOU HAVE NOT RELIED ON ANY ORAL OR WRITTEN INFORMATION OR ADVICE, WHETHER GIVEN BY XILINX, OR ITS AGENTS OR EMPLOYEES. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DESIGN, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND NONINFRINGEMENT OF THIRD-PARTY RIGHTS.

IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOST DATA AND LOST PROFITS, ARISING FROM OR RELATING TO YOUR USE OF THE DESIGN, EVEN IF YOU HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. THE TOTAL CUMULATIVE LIABILITY OF XILINX IN CONNECTION WITH YOUR USE OF THE DESIGN, WHETHER IN CONTRACT OR TORT OR OTHERWISE, WILL IN NO EVENT EXCEED THE AMOUNT OF FEES PAID BY YOU TO XILINX HEREUNDER FOR USE OF THE DESIGN. YOU ACKNOWLEDGE THAT THE FEES, IF ANY, REFLECT THE ALLOCATION OF RISK SET FORTH IN THIS AGREEMENT cc THAT XILINX WOULD NOT MAKE AVAILABLE THE DESIGN TO YOU WITHOUT THESE LIMITATIONS OF LIABILITY.

The Design is not designed or intended for use in the development of on-line control equipment in hazardous environments requiring failsafe controls, such as in the operation of nuclear facilities, aircraft navigation or communications systems, air traffic control, life support, or weapons systems ("High-Risk Applications"). Xilinx specifically disclaims any express or implied warranties of fitness for such High-Risk Applications. You represent that use of the Design in such High-Risk Applications is fully at your risk.

© 2002-2007 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, and other designated brands included herein are trademarks of Xilinx, Inc. PowerPC is a trademark of IBM Corp. and used under license. PCI, PCI-X, and PCI EXPRESS are registered trademarks of PCI-SIG. All other trademarks are the property of their respective owners.

### **Revision History**

The following table shows the revision history for this document.

| Date     | Version | Revision                     |

|----------|---------|------------------------------|

| 12/05/06 | 1.0     | Initial release.             |

| 02/26/07 | 1.1     | Added Spartan-3AN family.    |

| 04/02/07 | 1.2     | Added Spartan-3A DSP family. |

# Table of Contents

### Preface: About This Guide

| Guide Contents       | 21         |

|----------------------|------------|

| Additional Resources | 22         |

| Conventions          | 22         |

| Typographical        |            |

| Online Document      | <u>2</u> 3 |

### Section I: Designing with Spartan-3 Generation FPGAs

### **Chapter 1: Overview**

| <b>Introduction</b>                   |

|---------------------------------------|

| Spartan-3 Generation Platforms 28     |

| Spartan-3 Generation Features         |

| Spartan-3E/3A Additional Features 31  |

| Spartan-3A Additional Features        |

| Spartan-3AN Additional Features       |

| Spartan-3A DSP Additional Features 32 |

| Spartan-3 Generation Resources 32     |

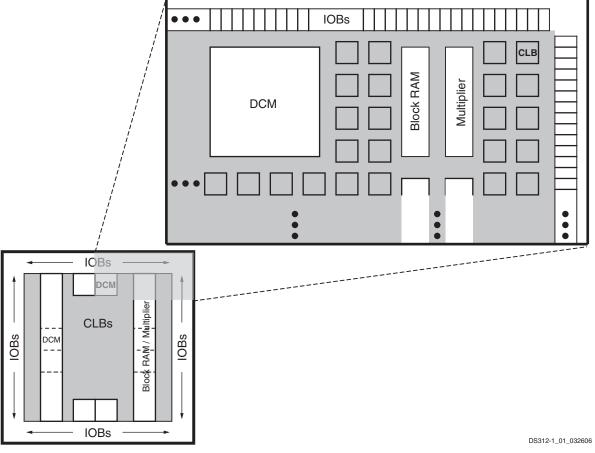

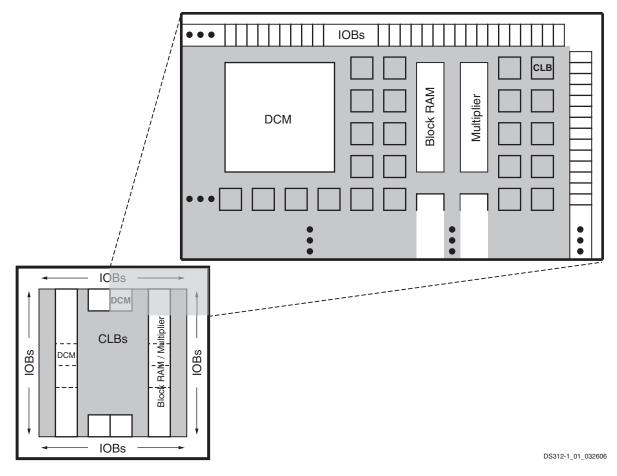

| Architectural Overview                |

| <b>Configuration</b>                  |

| I/O Capabilities                      |

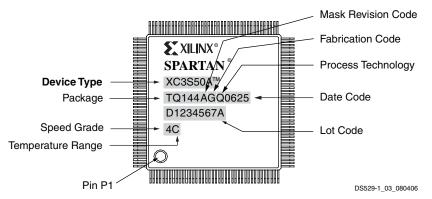

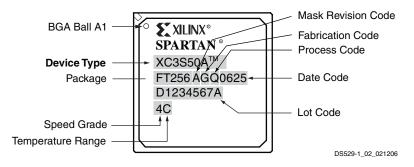

| Package Marking                       |

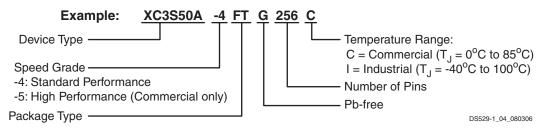

| Ordering Information                  |

### **Chapter 2: Using Global Clock Resources**

| Summary 43                                                                   | 3 |

|------------------------------------------------------------------------------|---|

| Introduction                                                                 | 3 |

| Global Clock Resource Differences between Spartan-3 Generation Families . 43 | 3 |

| Global Clock Resources                                                       | 1 |

| Clocking Infrastructure 44                                                   | 1 |

| <b>Clock Inputs</b>                                                          | 5 |

| Spartan-3A/3AN/3A DSP Clock Inputs 47                                        |   |

| Spartan-3E Clock Inputs 48                                                   |   |

| Spartan-3 Clock Inputs 49                                                    |   |

| Clock Inputs and DCMs 49                                                     | ) |

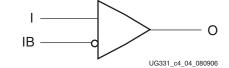

| Differential Clocks Using Two Inputs 49                                      |   |

| Using Dedicated Clock Inputs in a Design 50                                  | ) |

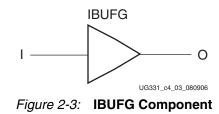

| IBUFG                                                                        |   |

| IBUFGDS                                                                      | ) |

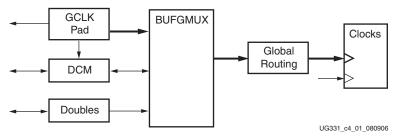

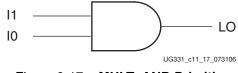

| Clock Buffers/Multiplexers                                                   | l |

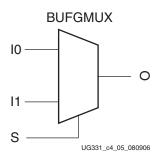

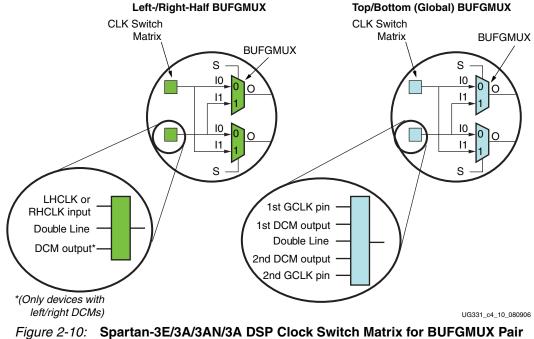

| BUFGMUX Multiplexing Details 52                                              | 2 |

| 1 0                                                                          |   |

| Using Clock Buffers/Multiplexers in a Design 52                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|

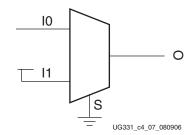

| BUFGMUX and BUFGMUX_1                                                                                                                                    |

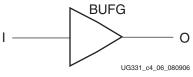

| BUFG                                                                                                                                                     |

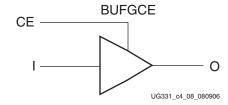

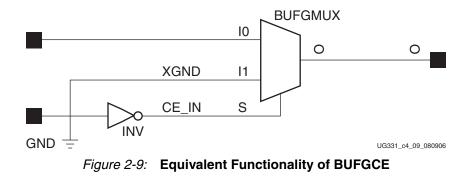

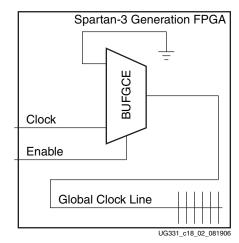

| BUFGCE and BUFGCE_1 53                                                                                                                                   |

| XST Synthesis of Clock Buffers 54                                                                                                                        |

| BUFGMUX Connection Details                                                                                                                               |

| BUFGMUX Inputs                                                                                                                                           |

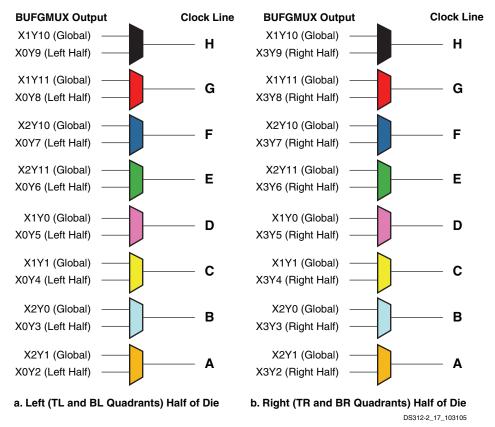

| BUFGMUX Outputs                                                                                                                                          |

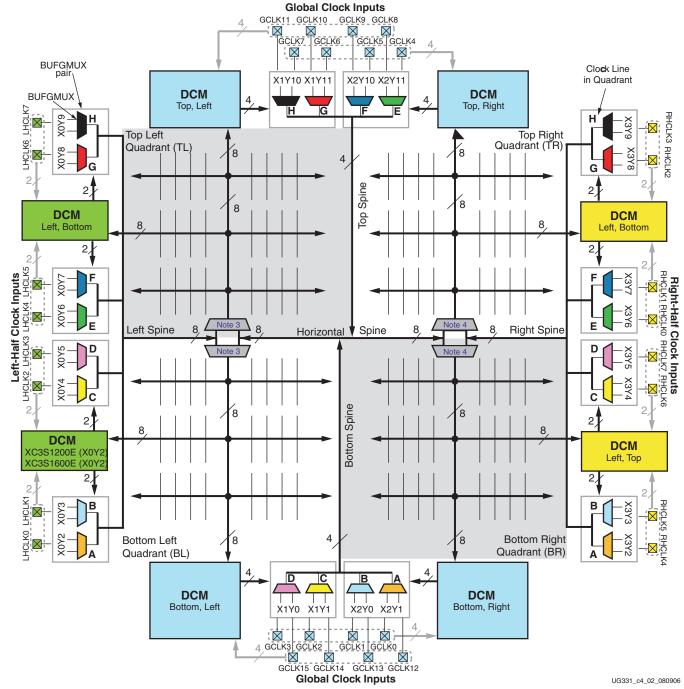

| Spartan-3 Global Clock Buffers 57                                                                                                                        |

| Quadrant Clock Routing       57         Choosing Top/Bottom and Left-/Right-Half Global Buffers       59         Spartan-3 Global Clock Routing       59 |

| Other Information                                                                                                                                        |

| Clock Power Consumption 59                                                                                                                               |

| Clock Setup and Hold Timing 59                                                                                                                           |

| Summary                                                                                                                                                  |

| Additional Information                                                                                                                                   |

### Chapter 3: Using Digital Clock Managers (DCMs)

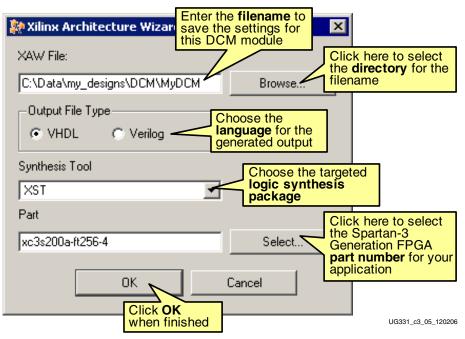

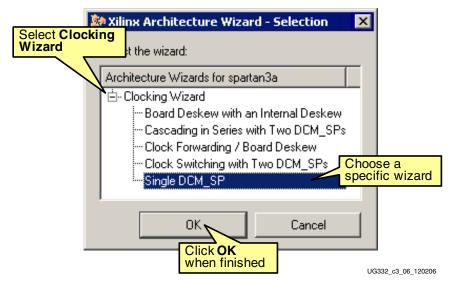

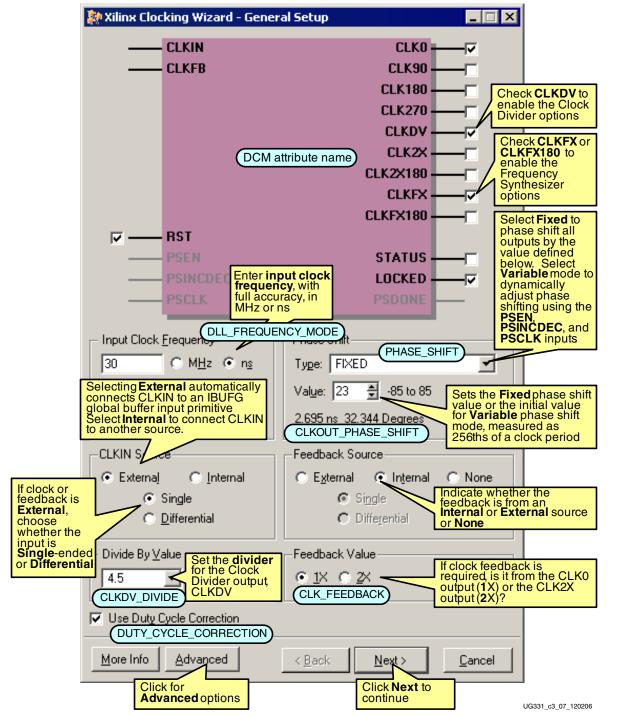

| General Setup                                                               | . 89 |

|-----------------------------------------------------------------------------|------|

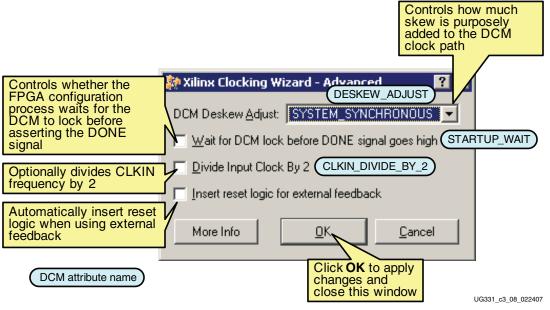

| Advanced Options                                                            | . 91 |

| Clock Buffers                                                               | . 92 |

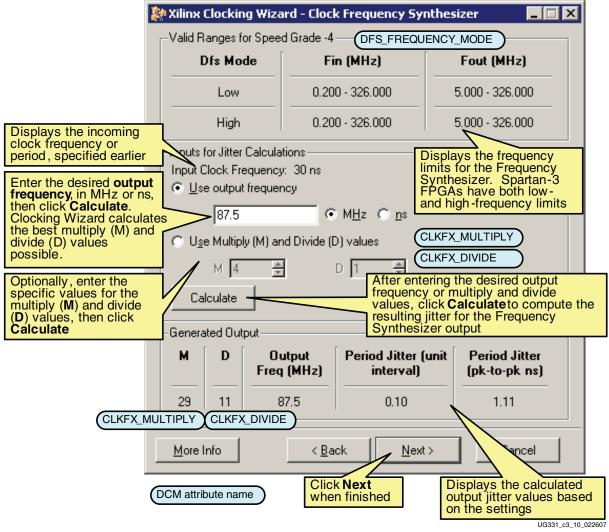

| Clock Frequency Synthesizer                                                 | . 93 |

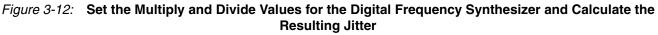

| Generating HDL Output                                                       | . 94 |

| VHDL and Verilog Instantiation                                              |      |

| Language Templates within Project Navigator.                                |      |

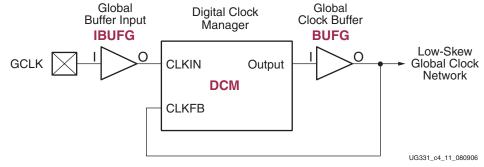

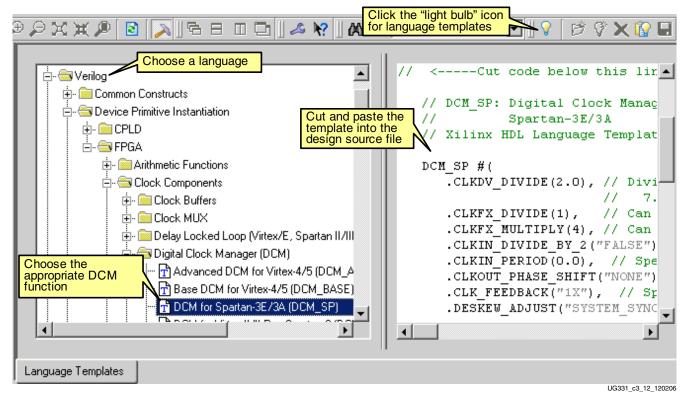

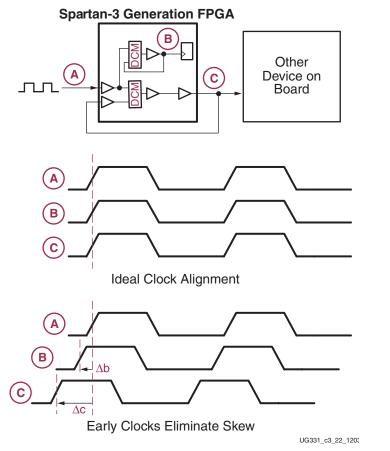

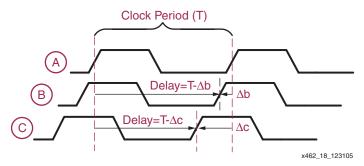

| Eliminating Clock Skew.                                                     |      |

| What is Clock Skew?                                                         |      |

| Clock Skew: The Performance Thief                                           |      |

| Make It Go Away!                                                            |      |

| Predicting the Future by Closely Examining the Past                         |      |

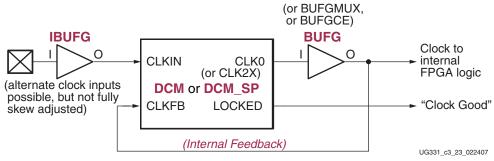

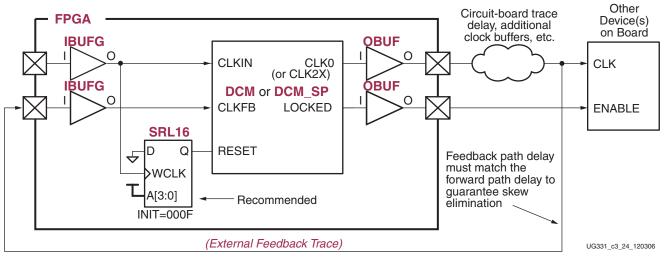

| Locked on Target                                                            |      |

| A Stable, Monotonic Clock Input.                                            |      |

| Feedback from a Reliable Source                                             |      |

| Removing Skew from an Internal Clock                                        |      |

| Removing Skew from an External Clock                                        |      |

| Reset DCM After Configuration                                               |      |

|                                                                             |      |

| What is a Dalay Locked Loop?                                                | 102  |

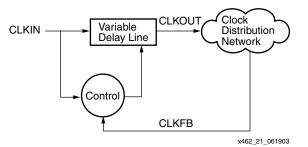

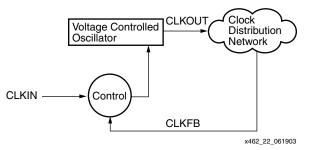

| What is a Delay-Locked Loop?                                                |      |

| Delay-Locked Loop (DLL)                                                     |      |

| Phase-Locked Loop (PLL)                                                     |      |

| Implementation.                                                             |      |

| DLL vs. PLL                                                                 |      |

| Skew Adjustment                                                             |      |

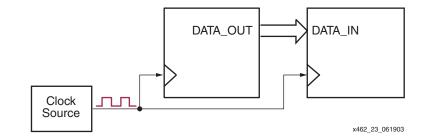

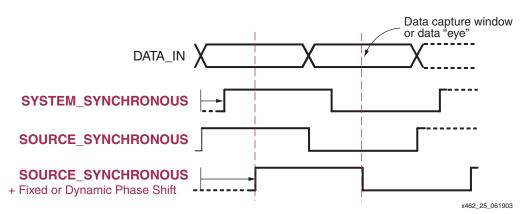

| System Synchronous                                                          |      |

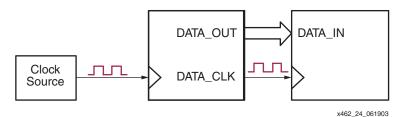

| Source Synchronous                                                          |      |

| Timing Comparisons                                                          |      |

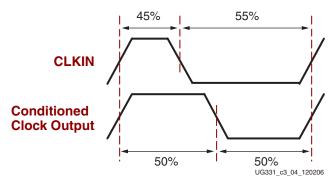

| Clock Conditioning                                                          |      |

| Spartan-3E and Spartan-3A/3AN/3A DSP FPGA Output Clock Conditioning         |      |

| Spartan-3 FPGA Output Clock Conditioning                                    | 107  |

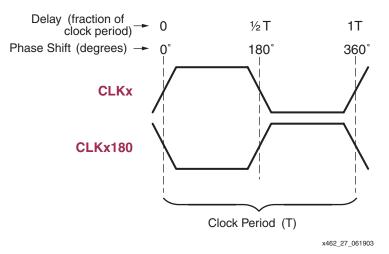

| Phase Shifting – Delaying Clock Outputs by a Fraction of a Period           | 108  |

| Half-Period Phase Shifted Outputs                                           |      |

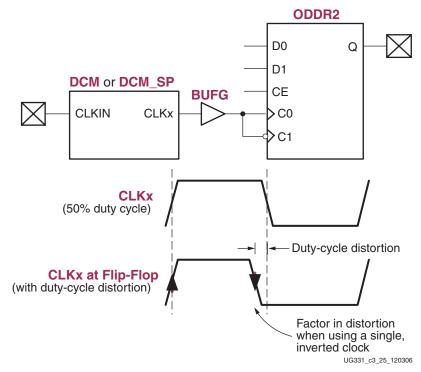

| Half-Period Phase Shift Outputs Reduce Duty-Cycle Distortion                | 110  |

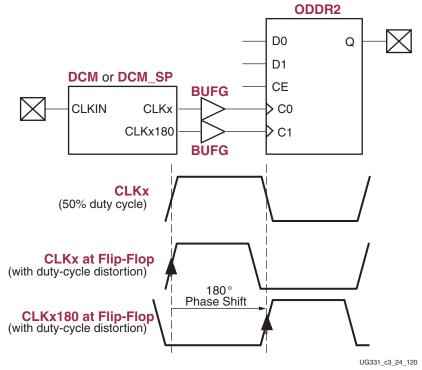

| Dual-Data Rate (DDR) Clocking Example                                       | 110  |

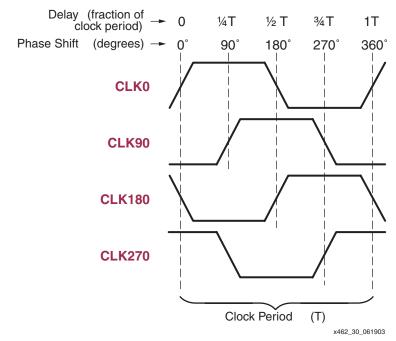

| Quadrant Phase Shifted Outputs                                              | 111  |

| Output Availability Depends on DLL Frequency Mode                           | 112  |

| Spartan-3 FPGA: Optional 50/50 Duty Cycle Correction                        | 112  |

| Four Phases, Delayed Clock Edges, Phased Pulses                             | 113  |

| Fine Phase Shifting                                                         | 113  |

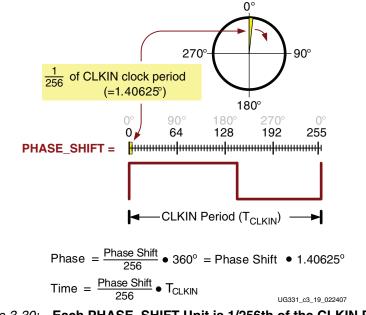

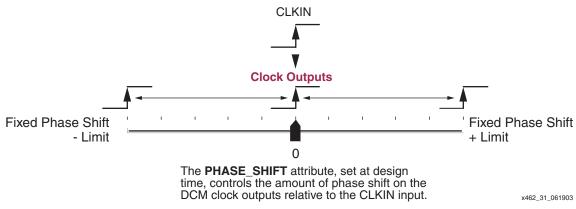

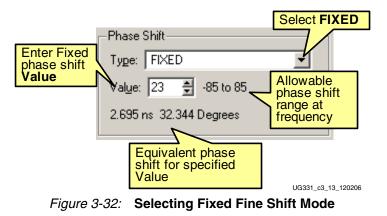

| Fixed Fine Phase Shifting                                                   | 114  |

| Fixed Fine Phase Shift Range                                                | 114  |

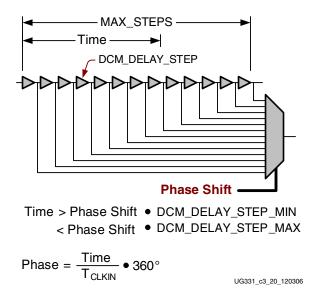

| Minimum Phase Shift Size                                                    | 116  |

| Other Design Considerations                                                 | 116  |

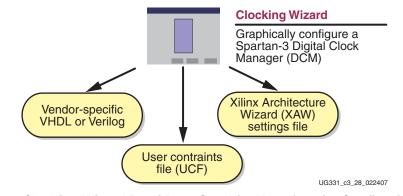

| Clocking Wizard                                                             | 116  |

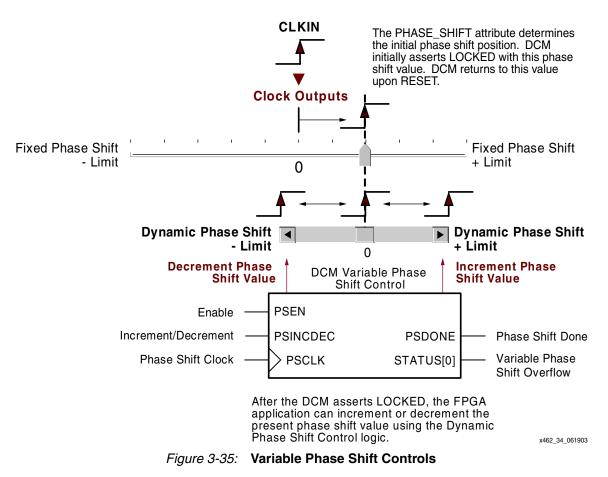

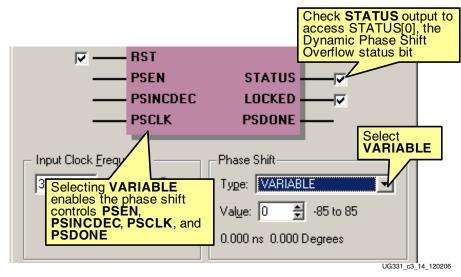

| Variable Fine Phase Shifting                                                |      |

| Important Differences Between Spartan-3 Generation FPGA Families.           |      |

| Spartan-3E and Spartan-3A/3AN/3A DSP Variable Phase Shift Operations        |      |

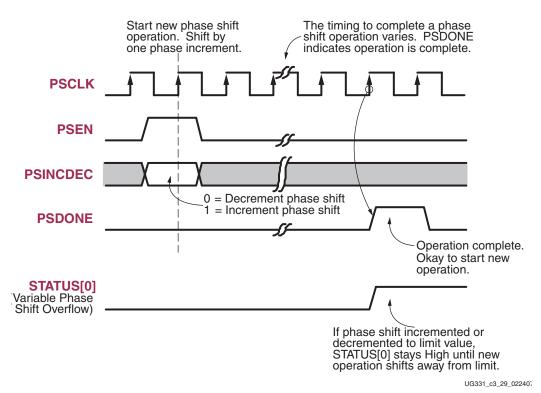

| Operation                                                                   |      |

| Variable Fine Phase Shift Range                                             |      |

| Spartan-3 FPGA Family Variable Phase Shift Range                            |      |

| Spartan-3E and Spartan-3A/3AN/3A DSP FPGA Family Variable Phase Shift Range |      |

| Controls                                                                    |      |

| Clocking Wizard                                                                  | . 123 |

|----------------------------------------------------------------------------------|-------|

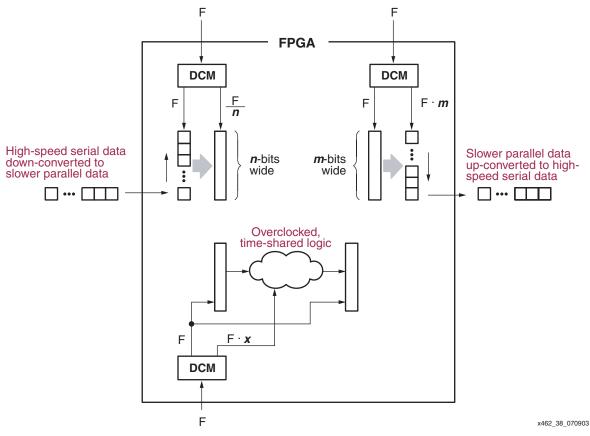

| Example Applications                                                             | . 123 |

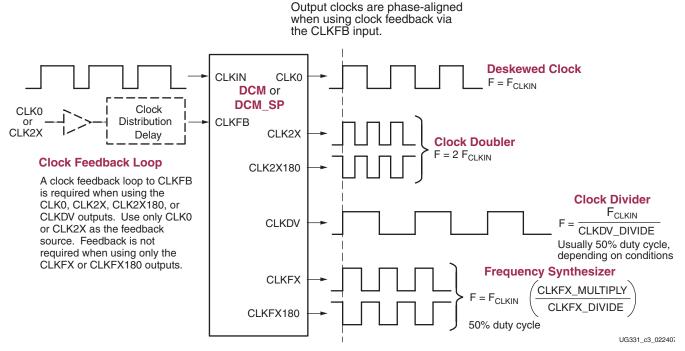

| Clock Multiplication, Clock Division, and Frequency Synthesis                    | . 123 |

| Frequency Synthesis Applications                                                 |       |

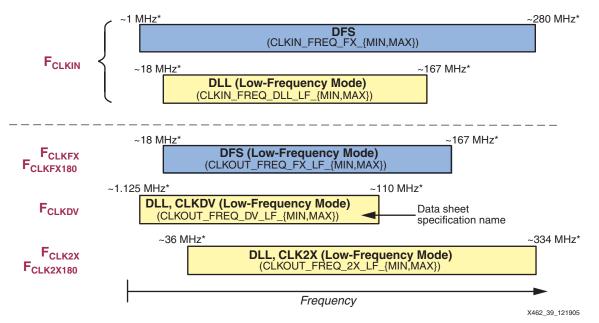

| Input and Output Clock Frequency Restrictions                                    | . 126 |

| Clock Doubler (CLK2X, CLK2X180)                                                  | . 127 |

| Clock Divider (CLKDV)                                                            | . 128 |

| CLKDV Clock Conditioning                                                         |       |

| CLKDV Jitter Depends on Frequency Mode and Integer or Non-Integer Value          | 130   |

| Clocking Wizard                                                                  |       |

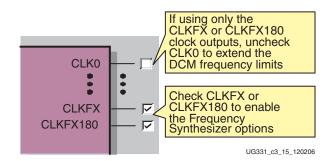

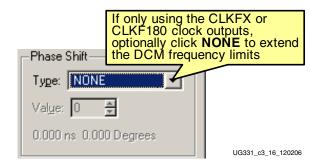

| Frequency Synthesizer (CLKFX, CLKFX180)                                          |       |

| Clocking Wizard                                                                  | . 132 |

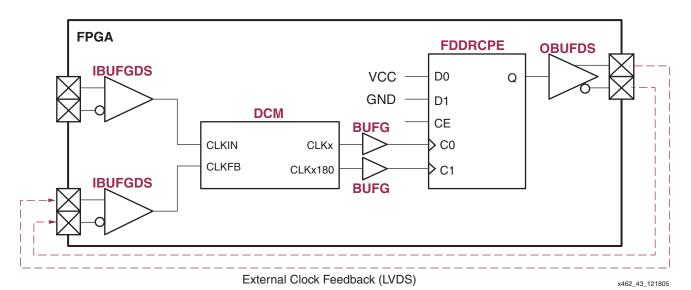

| Clock Forwarding, Mirroring, Rebuffering                                         | 133   |

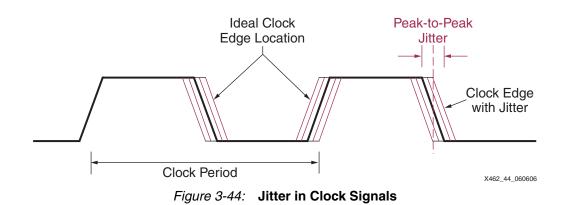

| Clock Jitter or Phase Noise                                                      | . 134 |

| What is Clock Jitter?                                                            |       |

| What Causes Clock Jitter?                                                        |       |

| Understanding Clock Jitter Specifications                                        |       |

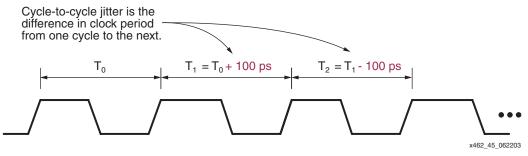

| Cycle-to-Cycle Jitter                                                            | 135   |

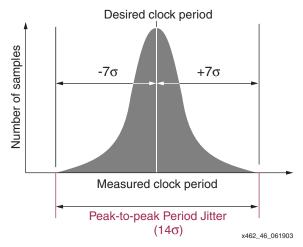

| Period Jitter                                                                    | 136   |

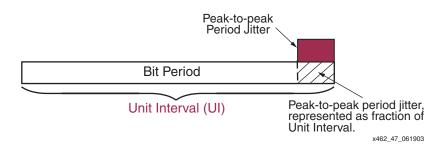

| Unit Interval (UI)                                                               | 136   |

| Calculating Total Jitter                                                         | . 137 |

| Adding Input Jitter to DLL Output Jitter                                         |       |

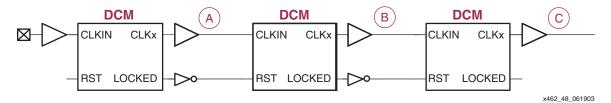

| Calculating Jitter for Cascaded DCMs                                             |       |

| Example 1: All DCMs Use DLL Outputs                                              |       |

| Example 2: Some DCMs Use the CLKFX or CLKFX180 Outputs                           |       |

| Cascaded DCM Design Recommendations                                              |       |

| Jitter Effect on System Performance                                              |       |

| Example                                                                          |       |

| Recommended Design Practices to Minimize Clock Jitter                            |       |

| Properly Design the Power Distribution System                                    |       |

| Properly Design the Printed Circuit Board                                        |       |

| Obey Simultaneous Switching Output (SSO) Recommendations                         |       |

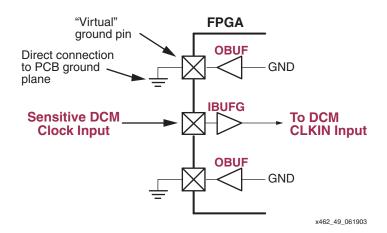

| Optionally Place Virtual Ground Pins Around DCM Input and Output Connections     |       |

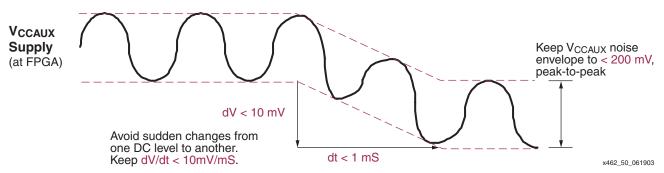

| V <sub>CCAUX</sub> Considerations for Improving Jitter Performance               |       |

| ,                                                                                |       |

| Miscellaneous Advanced Topics.                                                   |       |

| •                                                                                |       |

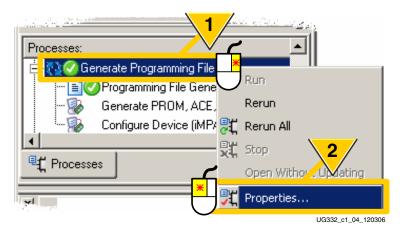

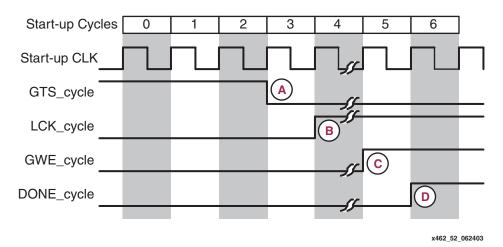

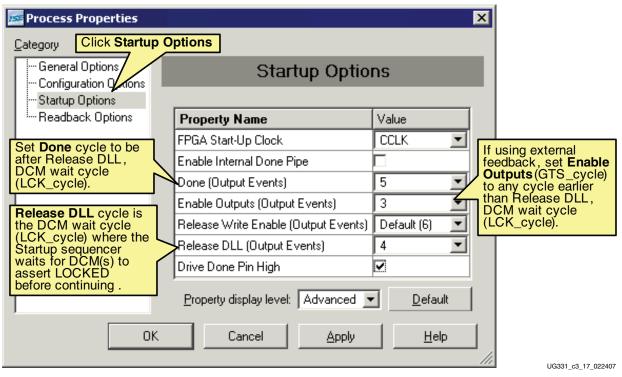

| Setting Bitstream Generation Options in Project Navigator                        |       |

| Setting Configuration Logic to Wait for DCM LOCKED Output                        |       |

| Reset DCM During Partial Reconfiguration or During Full Reconfiguration via JTAG |       |

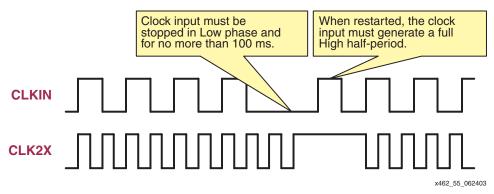

| Momentarily Stopping CLKIN                                                       |       |

| Related Materials and References                                                 |       |

|                                                                                  | 140   |

# Chapter 4: Using Block RAM

| Summary                                         | 149 |

|-------------------------------------------------|-----|

| Introduction                                    | 149 |

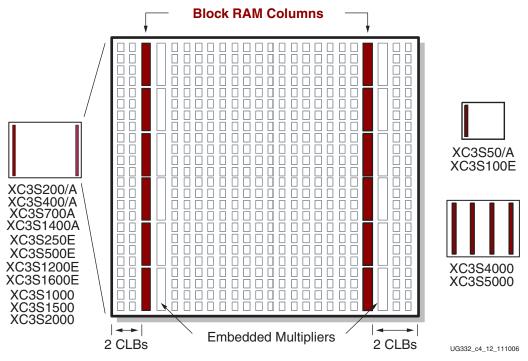

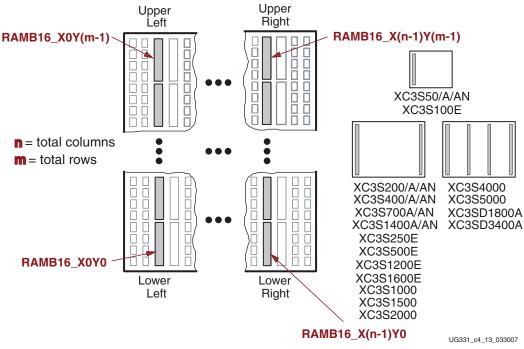

| Block RAM Location and Surrounding Neighborhood | 153 |

| Data Flows                                      | 154 |

| Signals                                         |     |

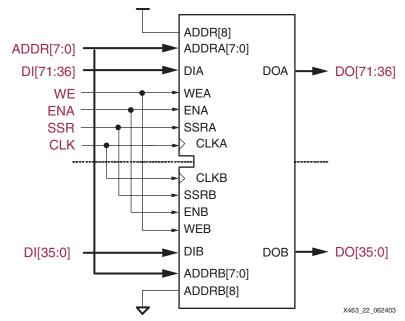

| Data Input Bus — DI[#:0] (DIA[#:0], DIB[#:0])                                              |

|--------------------------------------------------------------------------------------------|

| Data Output Bus — DO[#:0] (DOA[#:0], DOB[#:0]) 155                                         |

| Parity Inputs and Outputs                                                                  |

| Data Input Parity Bus — DIP[#:0] (DIPA[#:0], DIPB[#:0])                                    |

| Data Output Parity Bus — DOP[#:0] (DOPA[#:0], DOPB[#:0])                                   |

| Address Input                                                                              |

| Address Bus — ADDR[#:0] (ADDRA[#:0], ADDRB[#:0])                                           |

| Control Inputs                                                                             |

| Clock — CLK (CLKA, CLKB)                                                                   |

| Enable — EN (ENA, ENB)                                                                     |

| Write Enable — WE (WEA, WEB)                                                               |

|                                                                                            |

| Output Register Enable - REGCE (REGCEA, REGCEB) Spartan-3A DSP Only 159                    |

| Synchronous Set/Reset — SSR (SSRA, SSRB)                                                   |

| Output Register Reset - RST (RSTA, RSTB) - Spartan-3A DSP Only                             |

| Global Set/Reset — GSR                                                                     |

| Inverting Control Pins                                                                     |

| Unused Inputs                                                                              |

| <b>Attributes</b>                                                                          |

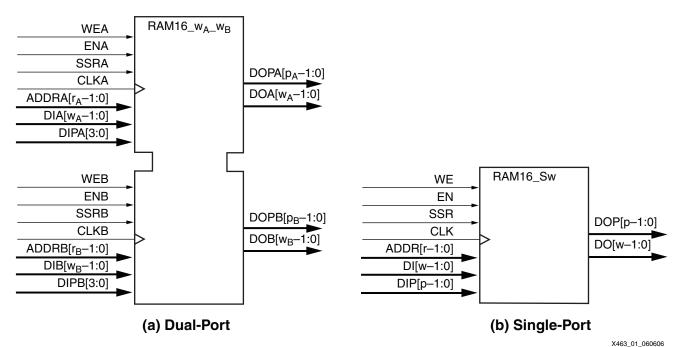

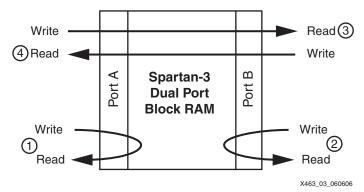

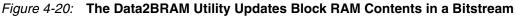

| Number of Ports                                                                            |

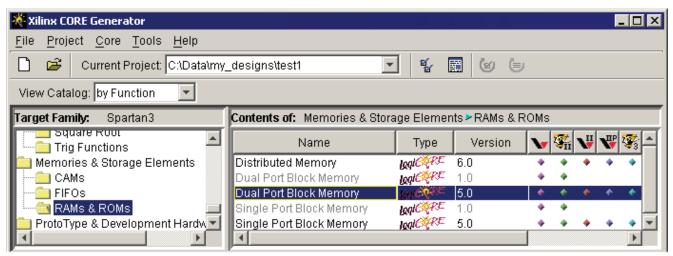

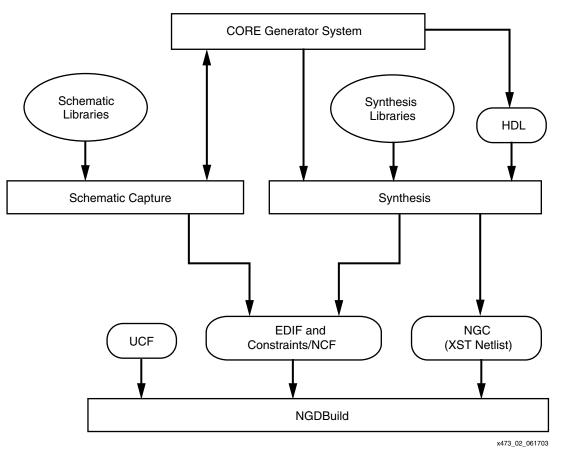

| CORE Generator System                                                                      |

| VHDL or Verilog Instantiation                                                              |

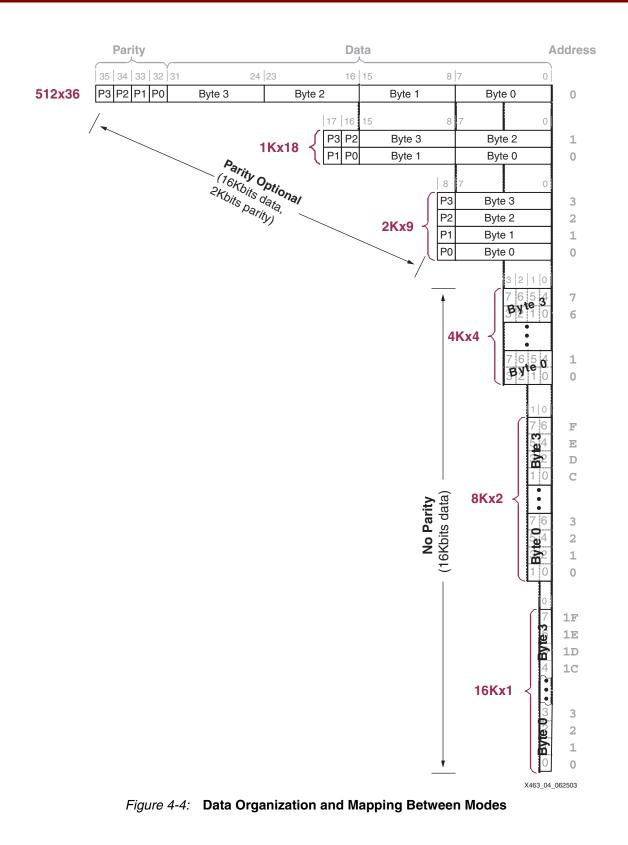

| Memory Organization/Aspect Ratio 162                                                       |

| CORE Generator System — Memory Size                                                        |

| VHDL or Verilog Instantiation                                                              |

| Address and Data Mapping Between Two Ports                                                 |

| Content Initialization                                                                     |

| CORE Generator System — Load Init File                                                     |

| VHDL or Verilog Instantiation — INIT_xx, INITP_xx                                          |

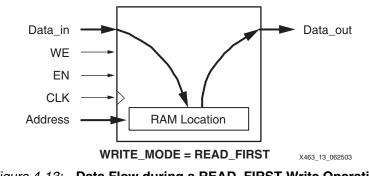

| Data Output Latch Initialization                                                           |

| CORE Generator System — Global Init Value                                                  |

| VHDL or Verilog Instantiation — INIT (INIT_A and INIT_B)                                   |

| Data Output Latch Synchronous Set/Reset Value                                              |

|                                                                                            |

| CORE Generator System — Init Value (SINIT)                                                 |

| VHDL or Verilog Instantiation — SRVAL (SRVAL_A and SRVAL_B)                                |

| Read Behavior During Simultaneous Write — WRITE_MODE                                       |

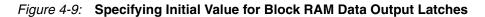

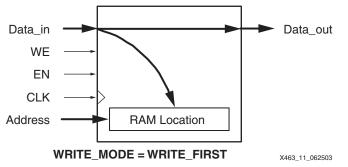

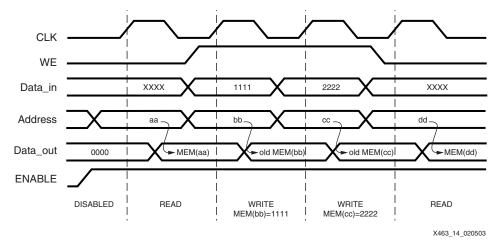

| WRITE_FIRST or Transparent Mode (Default)                                                  |

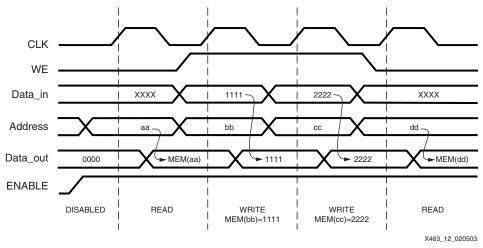

| READ_FIRST or Read-Before-Write Mode                                                       |

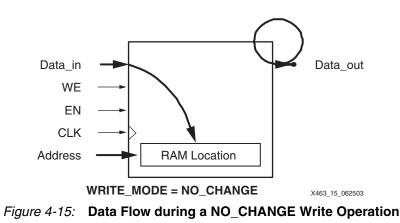

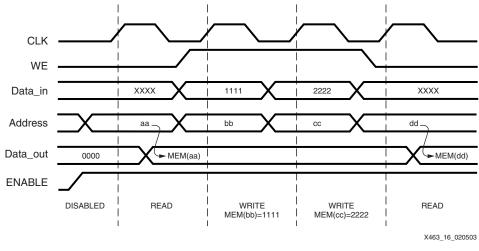

| NO_CHANGE Mode                                                                             |

| CORE Generator System — Write Mode 171                                                     |

| VHDL or Verilog Instantiation — WRITE_MODE                                                 |

| Location Constraints (LOC) 171                                                             |

| Block RAM Operation                                                                        |

| RAM Contents Initialized During Configuration 173                                          |

| Global Set/Reset Initializes Data Output Latches Immediately After Configuration or Global |

| Reset                                                                                      |

| Enable Input Activates or Disables RAM 173                                                 |

| Synchronous Set/Reset Initializes Data Output Latches                                      |

| Simultaneous Write and Synchronous Set/Reset Operations                                    |

| Read Operations Occur on Every Clock Edge When Enable is Asserted 174                      |

| Write Operations Always Have Simultaneous Read Operation, Data Output Latches Affected     |

| General Characteristics                                                                    |

| Functional Compatibility with Other Xilinx FPGA Families                                   |

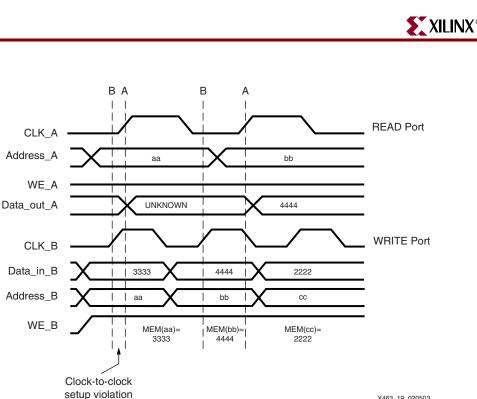

| Dual-Port RAM Conflicts and Resolution 175                                           |

|--------------------------------------------------------------------------------------|

| Timing Violation Conflicts 175                                                       |

| Simultaneous Writes to Both Ports with Different Data Conflicts 176                  |

| Write Mode Conflicts on Output Latches 177                                           |

| Conflict Resolution                                                                  |

| Block RAM Design Entry 177                                                           |

| Xilinx CORE Generator System 177                                                     |

| VHDL and Verilog Instantiation 178                                                   |

| Inferring Block RAM                                                                  |

| Instantiation Templates                                                              |

| Initialization in VHDL or Verilog Codes 179                                          |

| Block RAM Applications                                                               |

| Creating Larger RAM Structures                                                       |

| Block RAM as Read-Only Memory (ROM) 179                                              |

| FIFOs                                                                                |

| Storage for Embedded Processors                                                      |

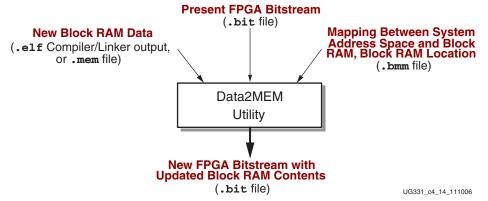

| Updating Block RAM/ROM Content by Directly Modifying Device Bitstream 180            |

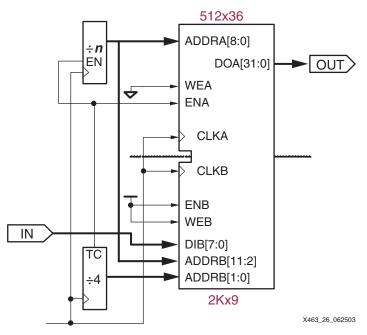

| Two Independent Single-Port RAMs Using One Block RAM 181                             |

| A 256x72 Single-Port RAM Using One Block RAM 182                                     |

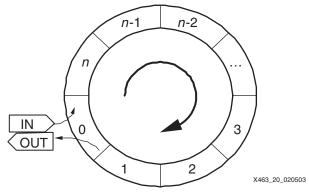

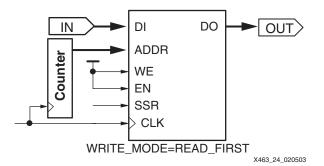

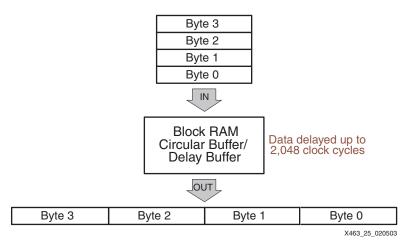

| Circular Buffers, Shift Registers, and Delay Lines                                   |

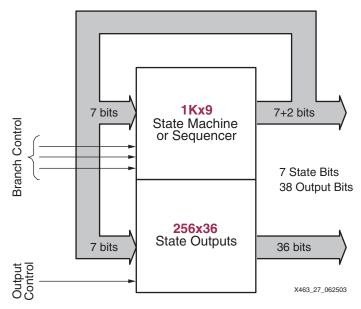

| Fast Complex State Machines and Microsequencers    185                               |

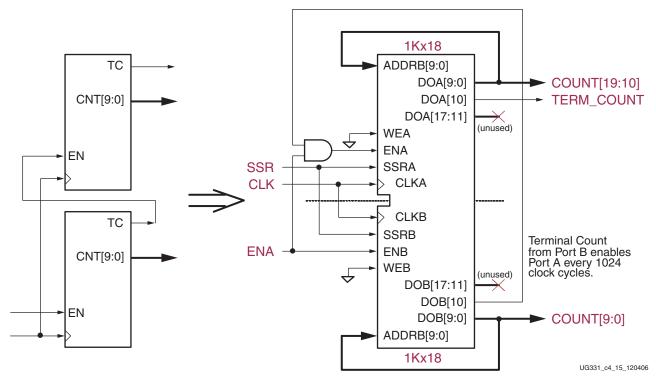

| Fast, Long Counters Using RAM    186                                                 |

| Four-Port Memory                                                                     |

| Content-Addressable Memory (CAM) 188                                                 |

| Implementing Logic Functions Using Block RAM 188                                     |

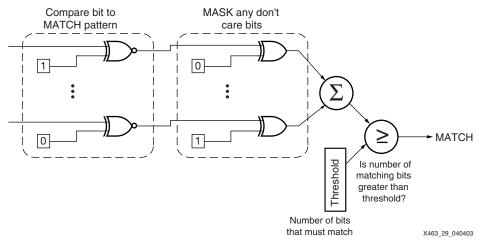

| Fuzzy Pattern Matching Circuit Example                                               |

| Mapping Logic into Block RAM Using MAP -bp Option                                    |

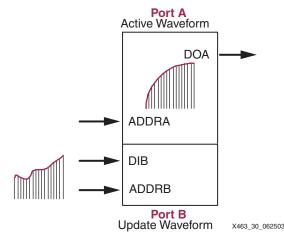

| Waveform Storage, Function Tables, Direct Digital Synthesis (DDS) Using Block RAM190 |

| Related Materials and References 191                                                 |

| <b>Conclusion</b>                                                                    |

| Appendix A: VHDL Instantiation Example 192                                           |

| Appendix B: Verilog Instantiation Example 195                                        |

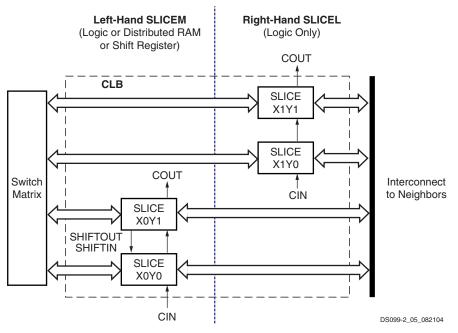

# Chapter 5: Using Configurable Logic Blocks (CLBs)

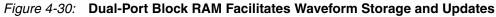

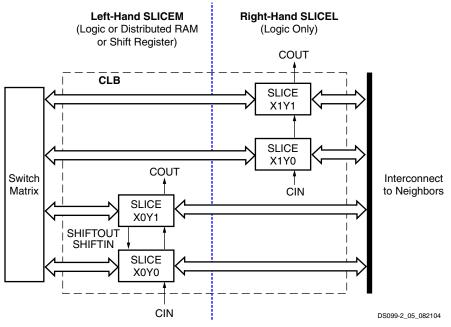

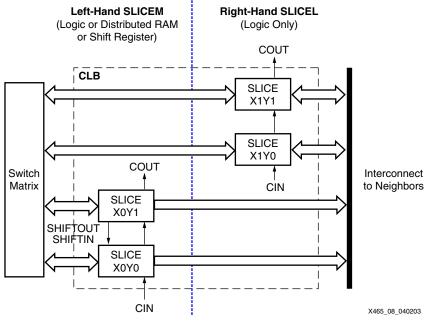

| CLB Overview                                          | 197 |

|-------------------------------------------------------|-----|

| CLB Array                                             | 197 |

| CLB Differences between Spartan-3 Generation Families |     |

| Slices                                                | 199 |

| Slice Location Designations                           | 201 |

| Slice Overview                                        | 201 |

| Logic Cells                                           |     |

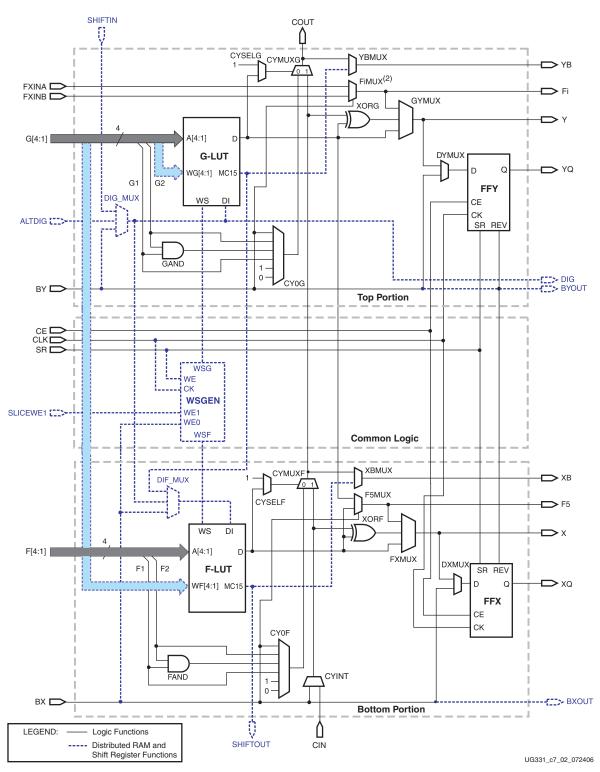

| Slice Details                                         |     |

| Main Logic Paths                                      |     |

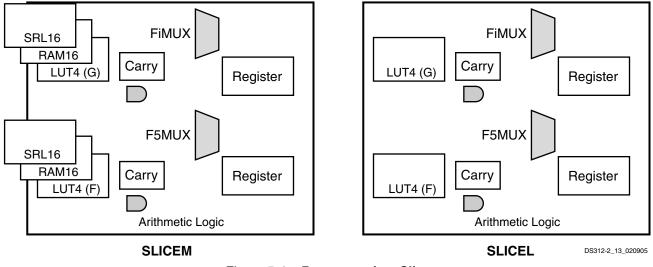

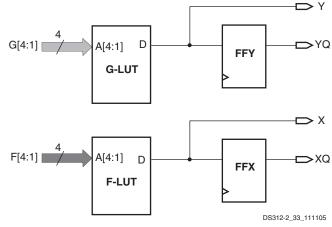

| Look-Up Tables                                        | 204 |

| Wide Multiplexers                                     |     |

| Carry and Arithmetic Logic                            | 205 |

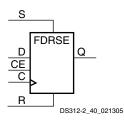

| Storage Elements                                      | 205 |

| Initialization                                        | 207 |

| Distributed RAM | 207 |

|-----------------|-----|

| Shift Registers | 207 |

### Chapter 6: Using Look-Up Tables as Distributed RAM

| Summary                                                           | . 209 |

|-------------------------------------------------------------------|-------|

| Introduction                                                      |       |

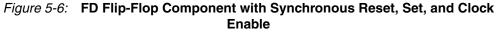

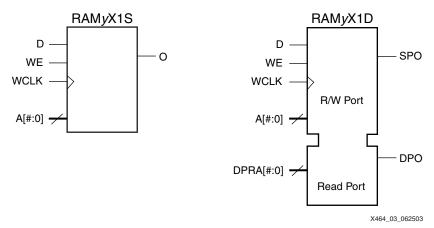

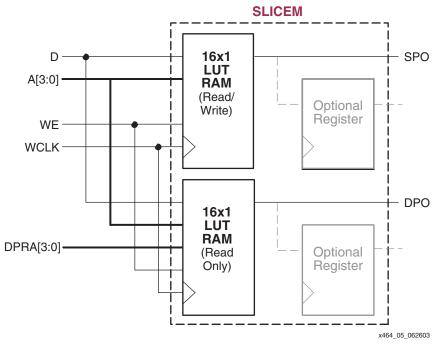

| Single-Port and Dual-Port RAMs                                    |       |

| Data Flow                                                         |       |

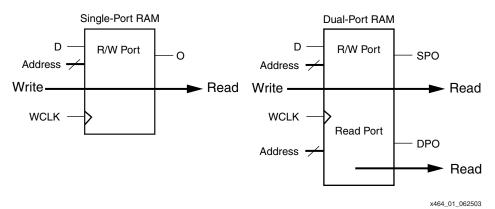

| Write Operations                                                  |       |

| Read Operation                                                    |       |

| Read During Write                                                 |       |

| Characteristics                                                   |       |

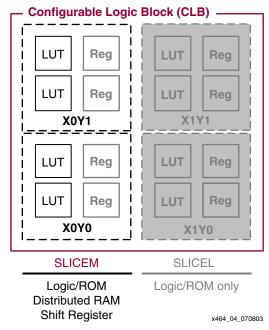

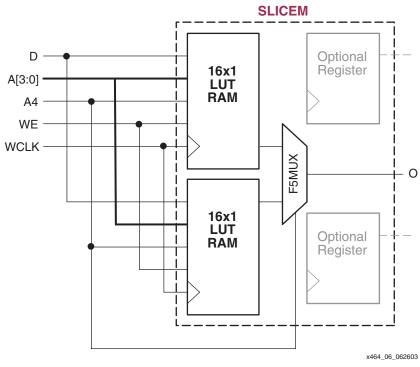

| Distributed RAM in the CLB                                        | . 211 |

| Distributed RAM Differences between Spartan-3 Generation Families | . 212 |

| Compatibility with Other Xilinx FPGA Families                     | . 213 |

| Library Primitives                                                | . 214 |

| Signal Ports                                                      | . 215 |

| Clock — WCLK                                                      |       |

| Enable — WE                                                       | . 215 |

| Address — A0, A1, A2, A3 (A4, A5, A6, A7)                         |       |

| Dual-Port Read Address — DPRA0, DPRA1, DPRA2, DPRA3               |       |

| Data In — D $\ldots$                                              |       |

| Data Out — O, SPO, and DPO                                        |       |

| Inverting Control Pins.                                           |       |

| Global Set/Reset — GSR                                            |       |

| Global Write Enable — GWE                                         |       |

| Attributes                                                        |       |

| Content Initialization — INIT                                     |       |

| Placement Location — LOC                                          |       |

| Distributed RAM Design Entry.                                     |       |

| Xilinx CORE Generator System                                      |       |

| VHDL and Verilog.                                                 |       |

| Inferring Distributed RAM                                         |       |

| Instantiation Templates                                           |       |

| Verilog Instantiation Template Example                            |       |

| Initialization in VHDL or Verilog Codes                           |       |

|                                                                   |       |

| Conclusion                                                        |       |

| Related Materials and References                                  | . 223 |

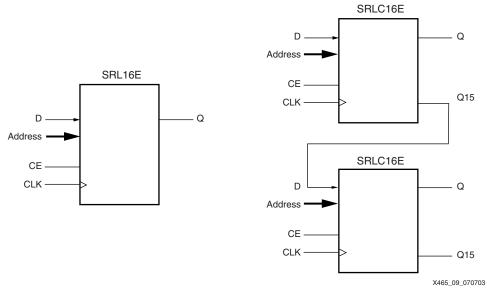

### Chapter 7: Using Look-Up Tables as Shift Registers (SRL16)

| Summary                                                          | 225 |

|------------------------------------------------------------------|-----|

| Shift Register Differences between Spartan-3 Generation Families | 225 |

| Introduction                                                     | 225 |

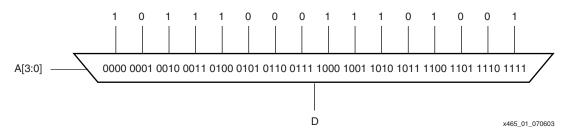

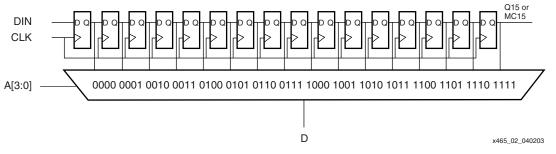

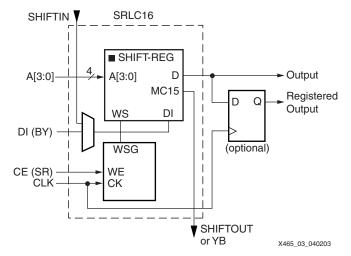

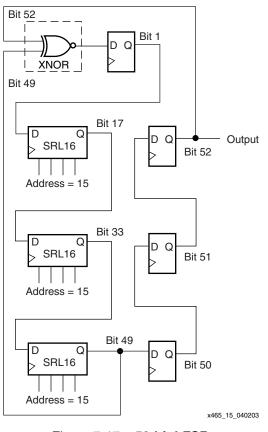

| Shift Register Architecture                                      | 226 |

| LUT Structure                                                    | 226 |

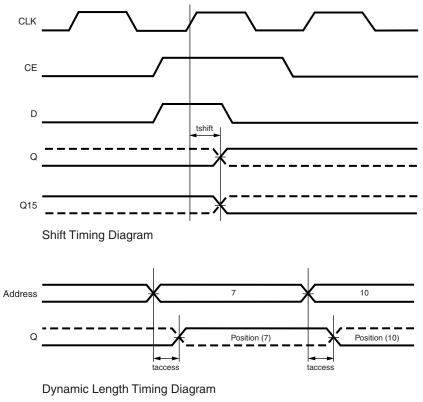

| Dynamic Length Adjustment                                        | 226 |

| Logic Cell Structure                                             | 226 |

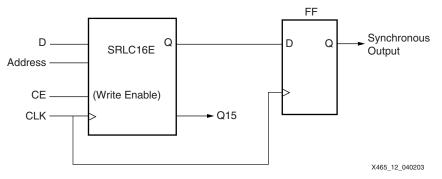

| Registered Output                       | 227       |

|-----------------------------------------|-----------|

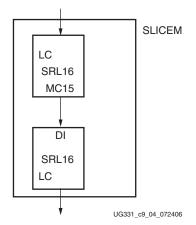

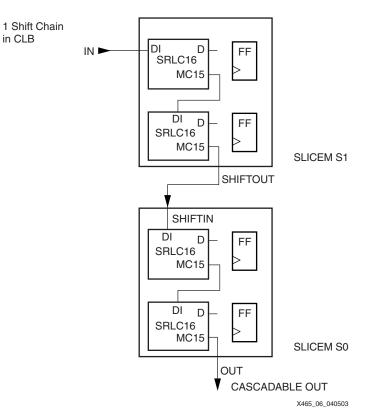

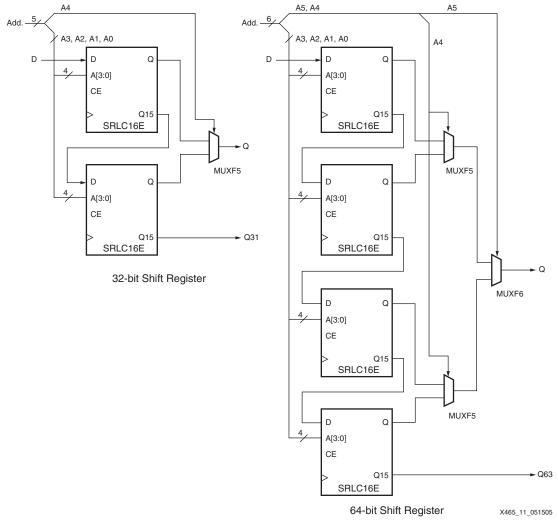

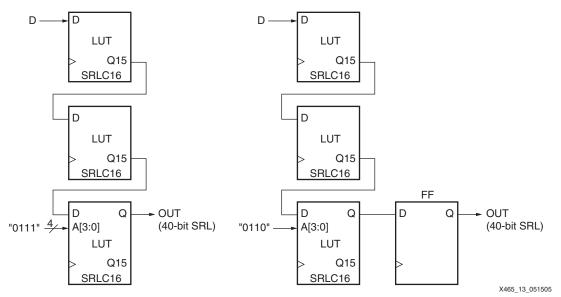

| Slice Structure                         | 227       |

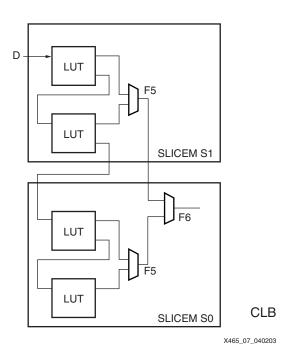

| CLB Structure                           | 228       |

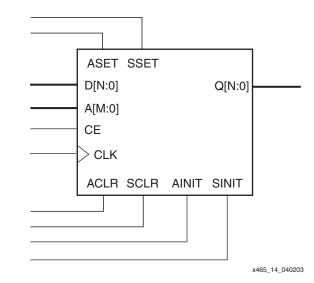

| Library Primitives                      | 230       |

| Initialization in VHDL and Verilog Code |           |

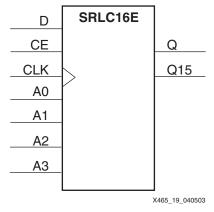

| Port Signals                            | 231       |

| Clock — CLK                             | 231       |

| Data In — D                             | 231       |

| Clock Enable — CE (optional)            | 231       |

| Address — A3, A2, A1, A0                | 231       |

| Data Out $-Q$                           | 232       |

| Data Out — Q15 (optional)               | 232       |

| Inverting Control Pins                  | 232       |

| GSR                                     |           |

| Attributes                              | 232       |

| Content Initialization — INIT           | 232       |

| Location Constraints                    | 232       |

| Shift Register Operations               | 233       |

| Data Flow                               |           |

| Shift Operation                         | 234       |

| Dynamic Read Operation                  | 234       |

| Static Read Operation                   |           |

| Characteristics                         | 235       |

| Shift Register Inference                | 235       |

| VHDL Inference Code                     | 236       |

| Verilog Inference Code                  | 236       |

| Shift Register Submodules               | 237       |

| Fully Synchronous Shift Registers       |           |

| Static-Length Shift Registers           |           |

| VHDL and Verilog Instantiation          |           |

| VHDL and Verilog Templates              | 239       |

| CORE Generator System                   | 241       |

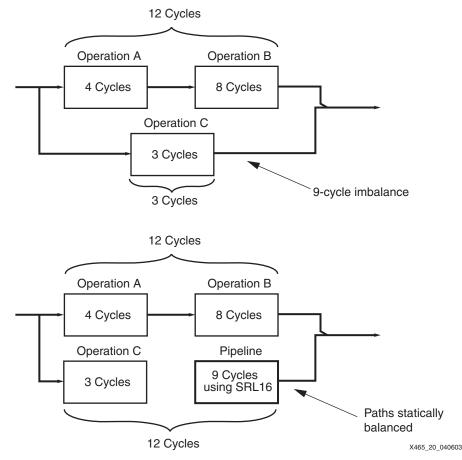

| Applications                            | 242       |

| Delay Lines                             |           |

| Linear Feedback Shift Registers         |           |

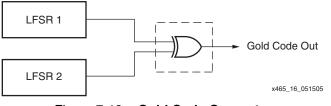

| Gold Code Generator                     |           |

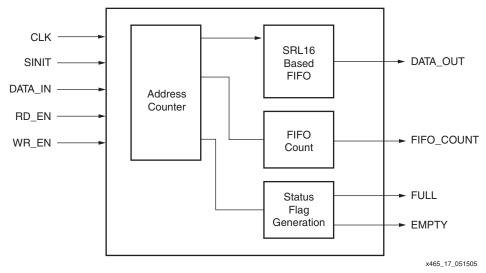

| FIFOs                                   |           |

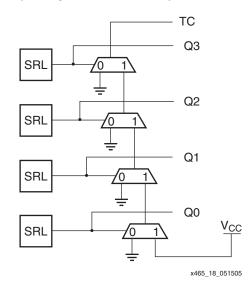

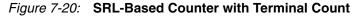

| Counters                                | 244       |

| Related Materials and References        |           |

| Conclusion                              |           |

|                                         | <b>4J</b> |

### **Chapter 8: Using Dedicated Multiplexers**

| Summary                                                                  | 247 |

|--------------------------------------------------------------------------|-----|

| Introduction                                                             | 247 |

| Dedicated Multiplexer Differences between Spartan-3 Generation Families. | 247 |

| Advantages of Dedicated Multiplexers                                     | 248 |

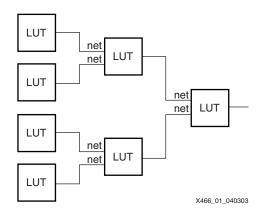

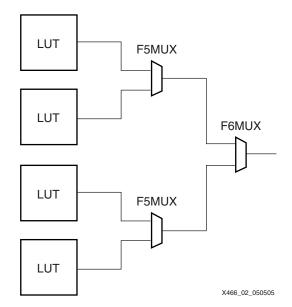

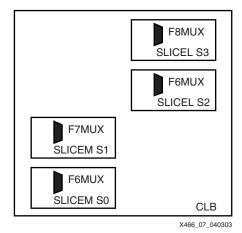

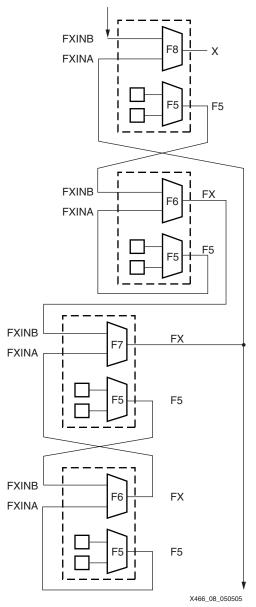

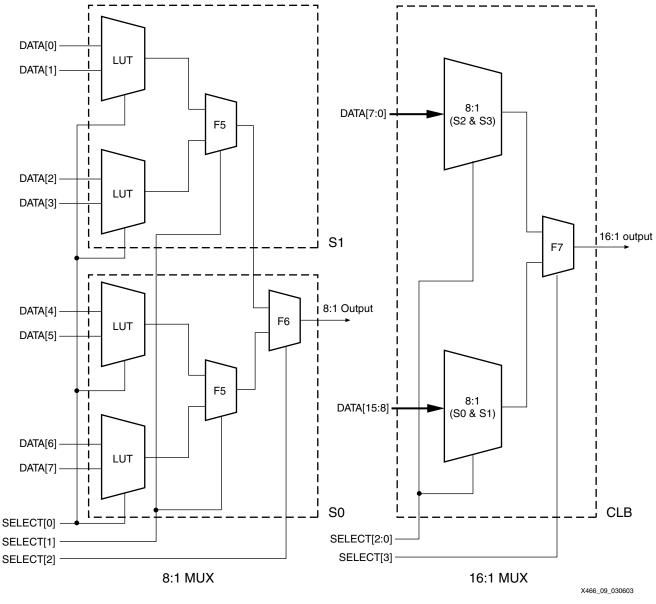

| CLB Multiplexer Resources                                                | 249 |

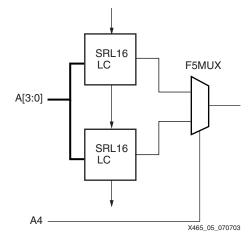

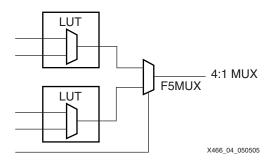

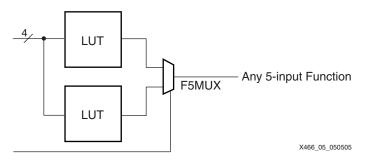

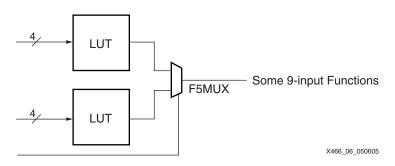

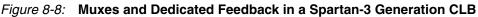

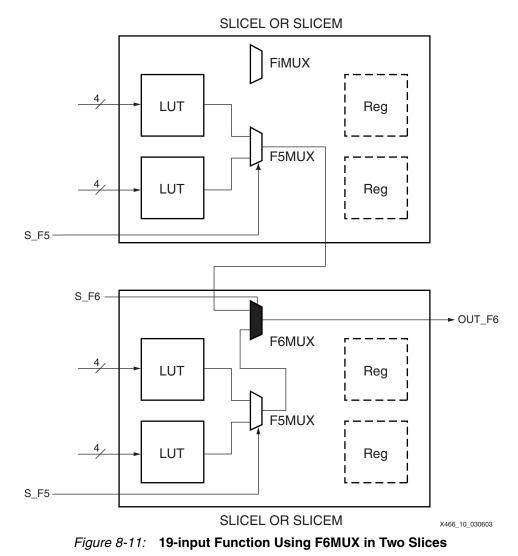

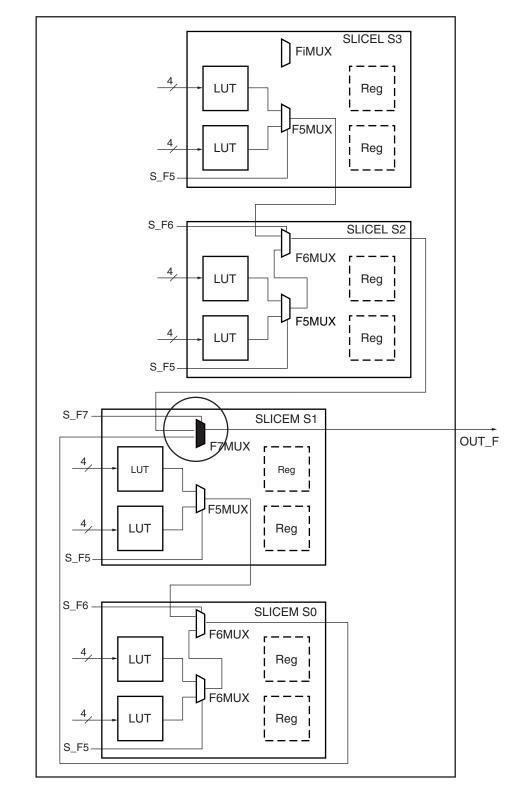

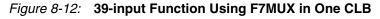

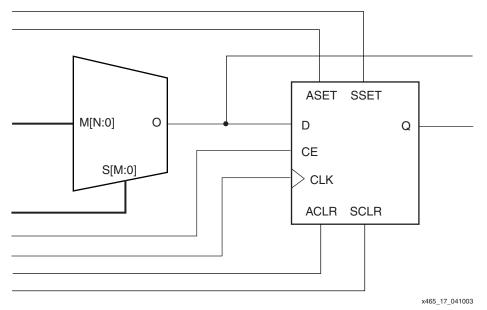

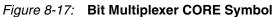

| F5MUX                                                                    | 249 |

| FiMUX                                                                    | 251 |

| Naming Conventions                                                       |     |

| Dedicated Local Routing                                                  | 252 |

| Mux Select Inputs                         |

|-------------------------------------------|

| Implementation Examples 253               |

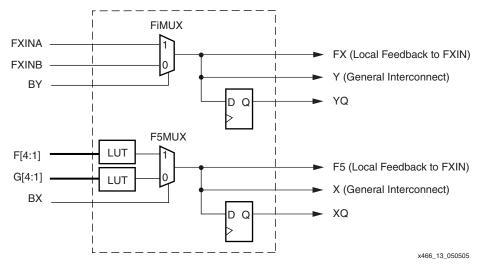

| Wide-Input Multiplexers                   |

| Wide-Input Functions                      |

| Timing Parameters                         |

| Programmable Polarity                     |

| Floorplanning Multiplexers 258            |

| Related Uses of Multiplexers              |

| Multiplexers and Three-State Buffers 259  |

| Using Memory in Place of Multiplexers 259 |

| Other Multiplexers                        |

| Designing with Multiplexers               |

| Inference                                 |

| Verilog Inference                         |

| VHDL Inference                            |

| Library Primitives                        |

| Enable Signals in Multiplexers 262        |

| Modeling Local Output Timing 263          |

| Submodules                                |

| Port Signals                              |

| Data In — DATA_I                          |

| Control In — SELECT_I                     |

| Data Out — DATA_O                         |

| Applications                              |

| VHDL and Verilog Instantiation    264     |

| VHDL and Verilog Submodules    265        |

| CORE Generator System                     |

| Summary                                   |

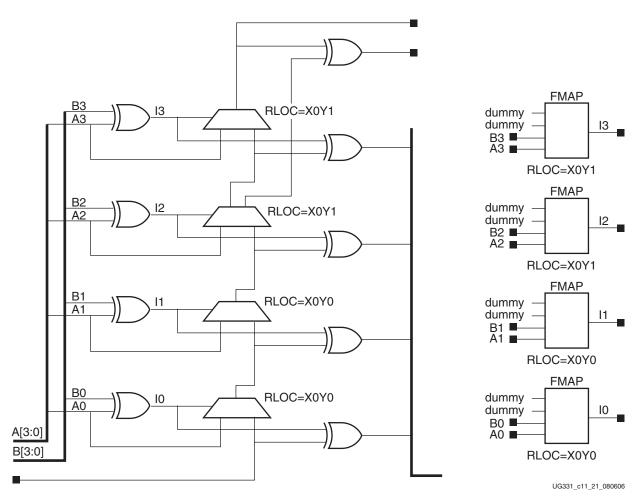

### Chapter 9: Using Carry and Arithmetic Logic

| Summary                                                                   | 271              |

|---------------------------------------------------------------------------|------------------|

| Introduction                                                              | 271              |

| Carry and Arithmetic Logic Differences between Spartan-3 Generation Famil | l <b>ies</b> 271 |

| Look-Ahead Carry Addition                                                 | 272              |

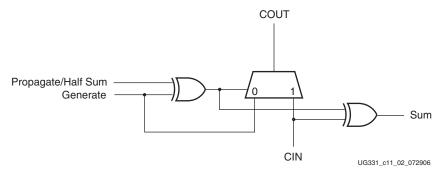

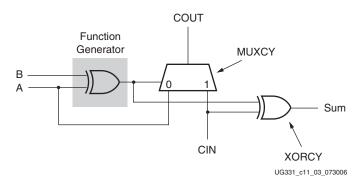

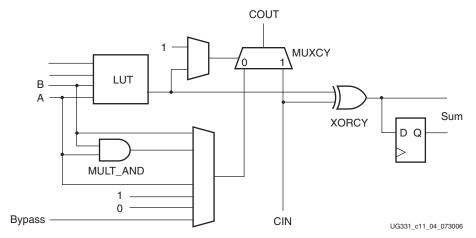

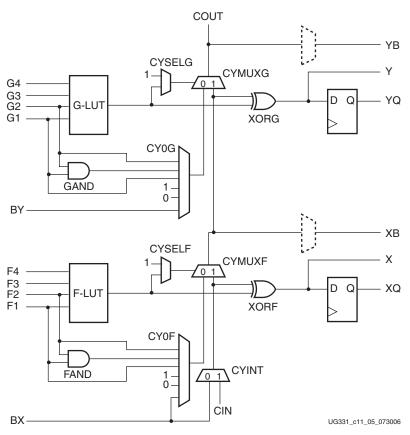

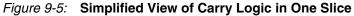

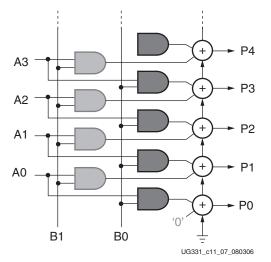

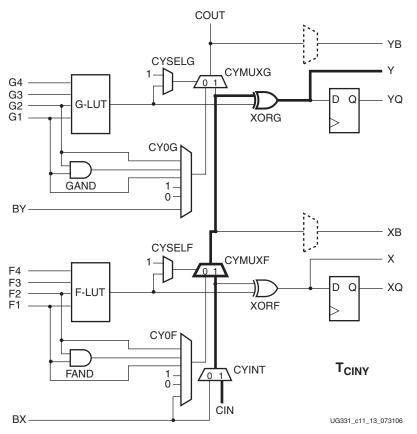

| Resource Details                                                          | 273              |

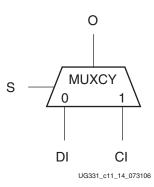

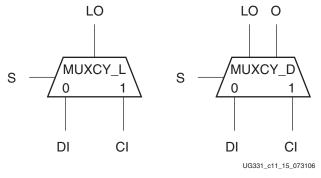

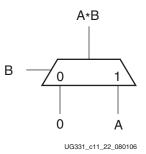

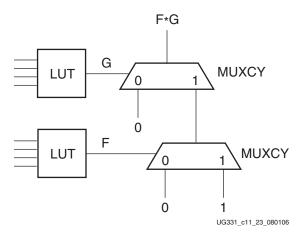

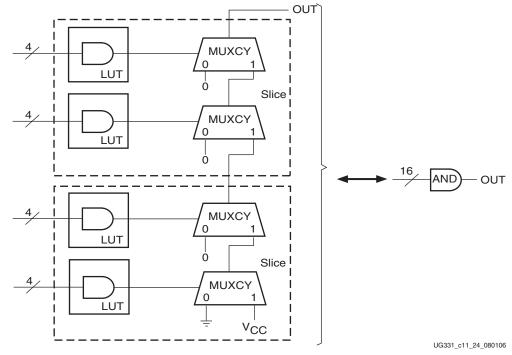

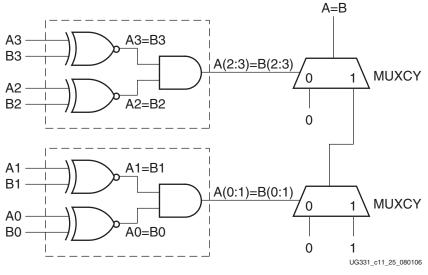

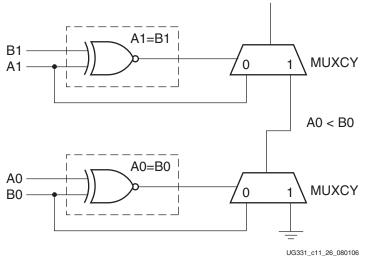

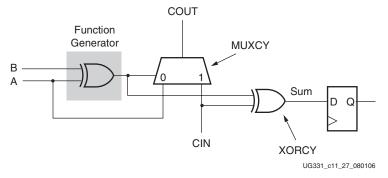

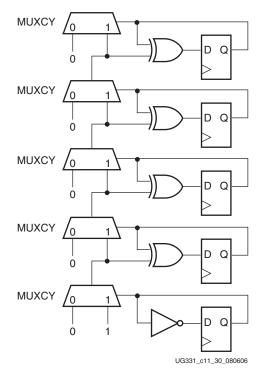

| MUXCY                                                                     | 275              |

| Carry Chain Bypass and Initialization                                     | 275              |

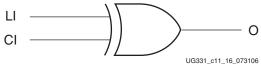

| XORCY                                                                     |                  |

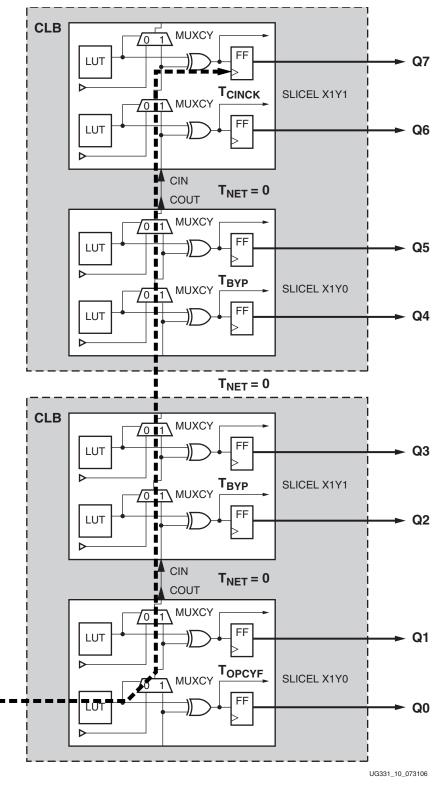

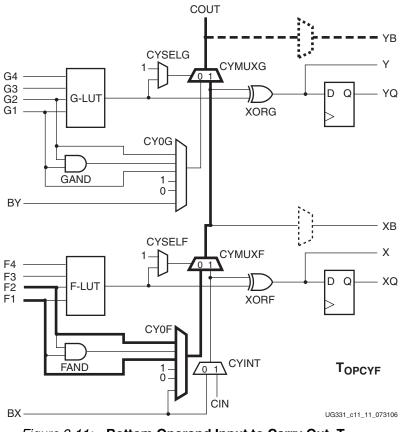

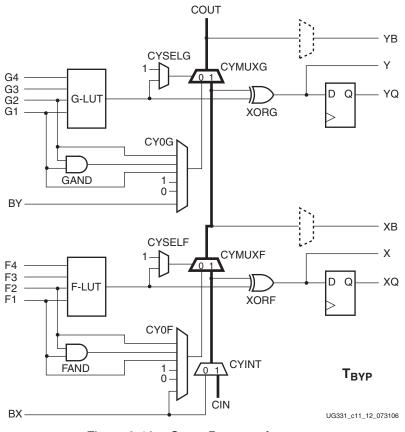

| Carry Logic Connections                                                   | 275              |

| Connections within a Slice                                                | 275              |

| Connections between Slices and CLBs                                       | 276              |

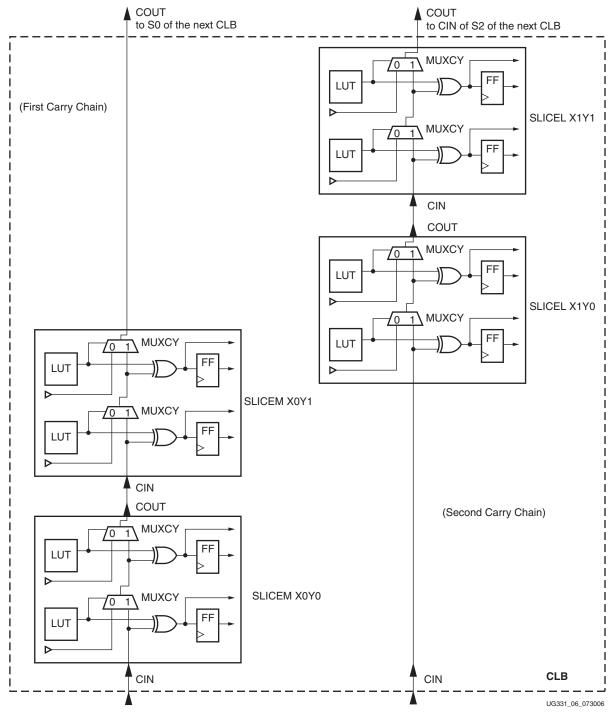

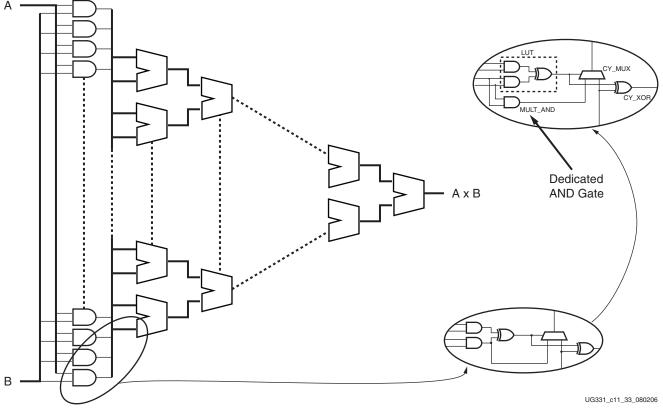

| Multiplication Resources                                                  | 279              |

| Component and Pin Names                                                   | 280              |

| Performance                                                               | 282              |

| Specifications                                                            | 286              |

| Designing with the Carry and Arithmetic Logic                             | 288              |

| Library Elements Using Carry                                              |                  |

| Primitives                                                                |                  |

| XORCY                                                                     | 290              |

|                                                                           |                  |

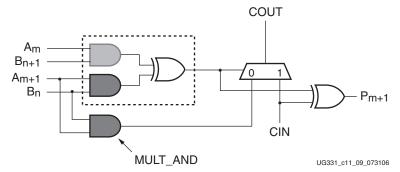

| MULT_AND                                    |

|---------------------------------------------|

| Emulating Virtex-II ORCY Components         |

| Macros                                      |

| Using the CORE Generator System             |

| Adder                                       |

| Accumulator                                 |

| Comparator                                  |

| Multiplier                                  |

| Logic Gates                                 |

| Carry and Synthesis Constraints 295         |

| MUX_STYLE Constraint                        |

| MULT_STYLE Constraint                       |

| Carry and Relative Location Constraints 296 |

| Carry and Floorplanning                     |

| Applications                                |

| Wide Gates                                  |

| Sum of Products                             |

| Comparators                                 |

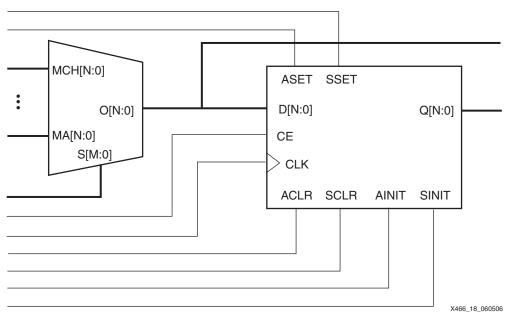

| Adders                                      |

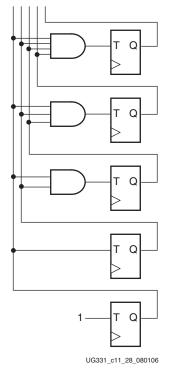

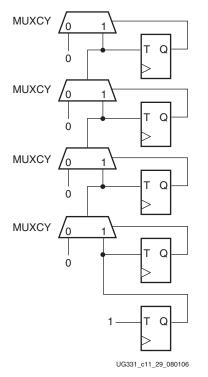

| Counters                                    |

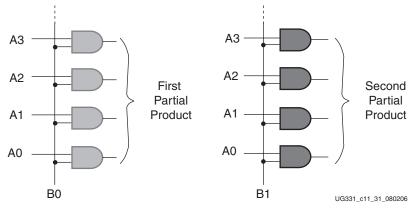

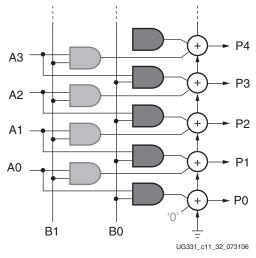

| Multipliers                                 |

| Optimizing Carry-Based Multipliers 305      |

| MULT_AND vs. MULT18X18                      |

| MULT_AND vs. CLB Logic 306                  |

| Other Types of Multipliers                  |

| Conclusion                                  |

| Related Materials and References 307        |

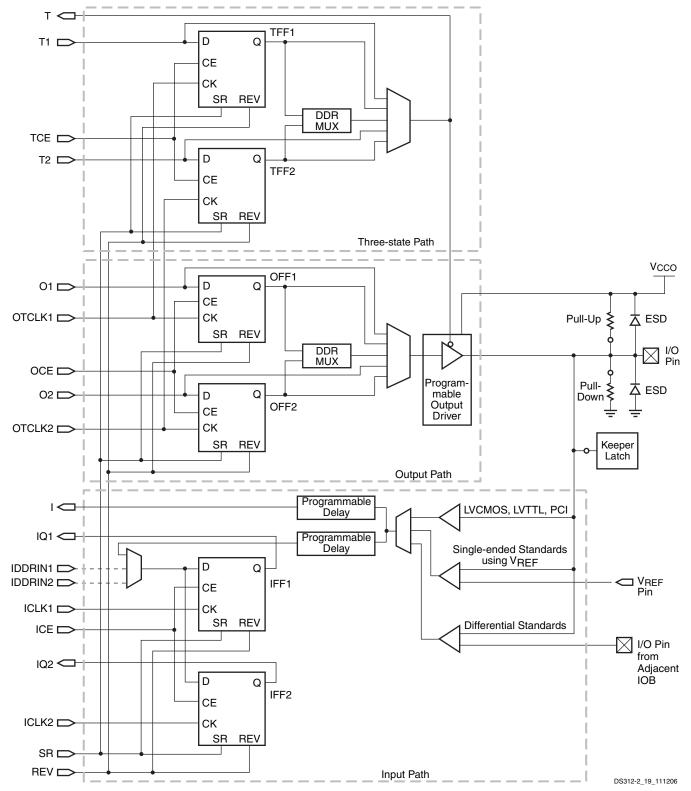

# Chapter 10: Using I/O Resources

| IOB Overview                                          |     |

|-------------------------------------------------------|-----|

| I/O Differences between Spartan-3 Generation Families |     |

| Number of Resources per Device                        | 312 |

| Input-Only Pins                                       |     |

| Package Footprint Compatibility                       |     |

| Summary of Differences                                |     |

| Design Entry                                          |     |

| Library Components                                    | 314 |

| Registered I/O                                        | 315 |

| Differential I/O                                      |     |

| IBUF                                                  |     |

| IBUFG                                                 |     |

| IBUFDS                                                |     |

| OBUF                                                  |     |

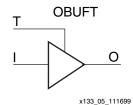

| OBUFT                                                 |     |

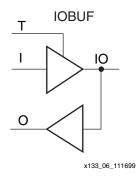

| IOBUF                                                 |     |

| DDR and Adjustable Delay I/O Components               |     |

| HDL Entry                                             |     |

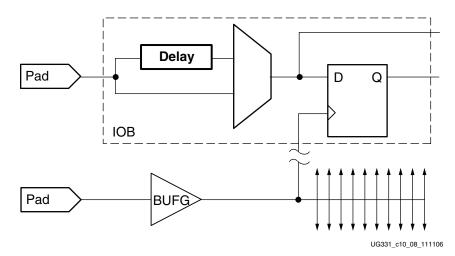

| Architectural Details                                 |     |

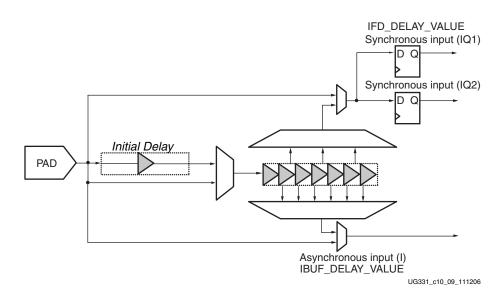

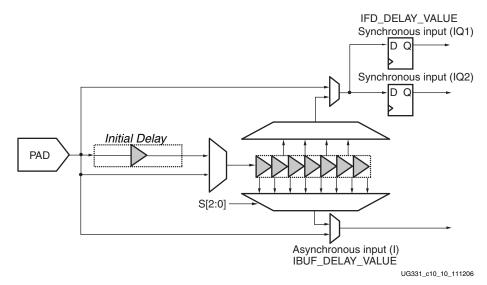

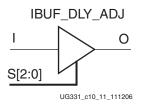

| Input Delay Functions                                 |     |

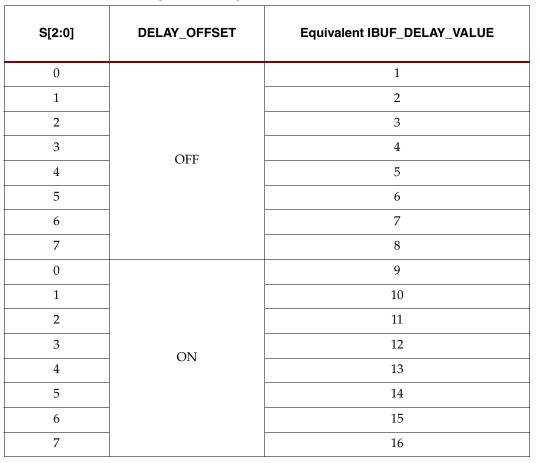

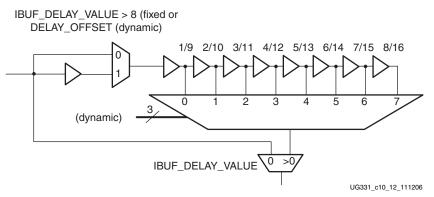

| Programmable Delay                                    |     |

| Dynamic Delay                                         |     |

#

| Storage Element Functions                                                        |

|----------------------------------------------------------------------------------|

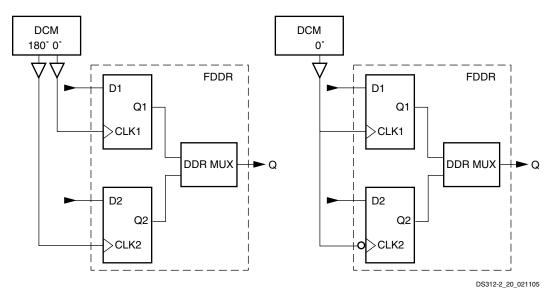

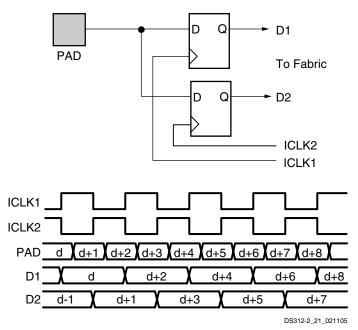

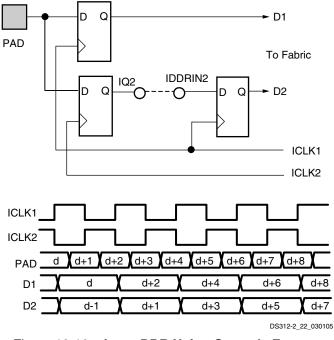

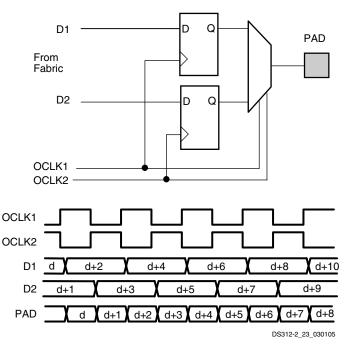

| Double-Data-Rate Transmission                                                    |

| Register Cascade Feature                                                         |

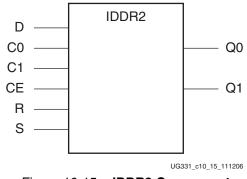

| IDDR2                                                                            |

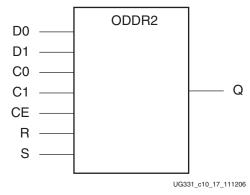

| ODDR2                                                                            |

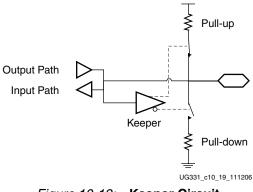

| Pull-Up and Pull-Down Resistors                                                  |

| FPGA Pull-Up Resistor Values                                                     |

| Keeper Circuit                                                                   |

| JTAG Boundary-Scan Capability                                                    |

| SelectIO Signal Standards                                                        |

| Overview of I/O Standards                                                        |

| LVTTL — Low-Voltage TTL                                                          |

| LVCMOS — Low-Voltage CMOS                                                        |

| PCI — Peripheral Component Interface                                             |

| GTL — Gunning Transceiver Logic Terminated                                       |

| GTL+ — Gunning Transceiver Logic Plus                                            |

| HSTL — High-Speed Transceiver Logic                                              |

| SSTL3 — Stub Series Terminated Logic for 3.3V                                    |

| SSTL25 — Stub Series Terminated Logic for 2.5V                                   |

| SSTL18 — Stub Series Terminated Logic for 1.8V                                   |

| LVDS — Low Voltage Differential Signal                                           |

| BLVDS — Bus LVDS                                                                 |

| LVPECL — Low Voltage Positive Emitter Coupled Logic                              |

| LDT - HyperTransport (formerly known as Lightning Data Transport)                |

| mini-LVDS                                                                        |

| LVDS Extended - Extended Mode LVDS                                               |

| RSDS - Reduced Swing Differential Signaling                                      |

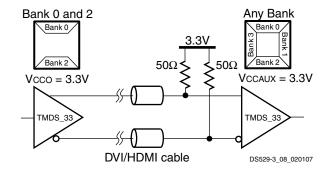

| TMDS - Transition Minimized Differential Signaling                               |

| PPDS - Point-to-Point Differential Signaling                                     |

| I/O Standard Differences between Spartan-3 Generation Families                   |

| Specifying an I/O Standard with the IOSTANDARD Attribute                         |

| Timing Analysis                                                                  |

| LVCMOS/LVTTL Slew Rate Control and Drive Strength                                |

| Simultaneously Switching Outputs                                                 |

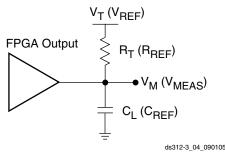

| HSTL/SSTL V <sub>REF</sub> Reference Voltage                                     |

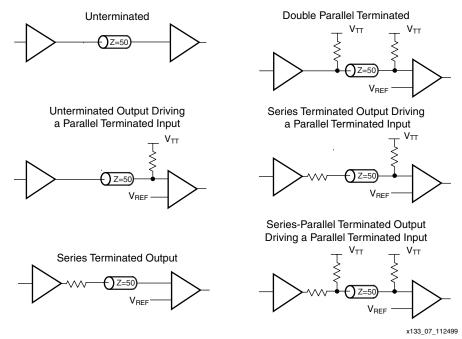

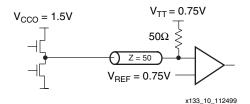

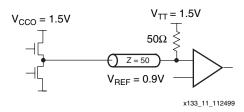

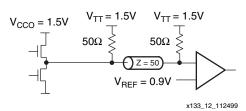

| Single-Ended I/O Termination Techniques                                          |

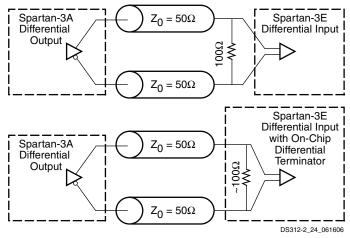

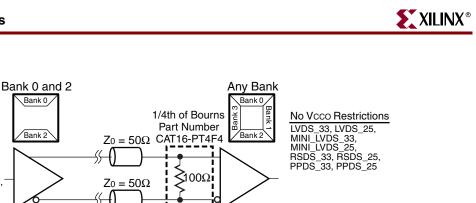

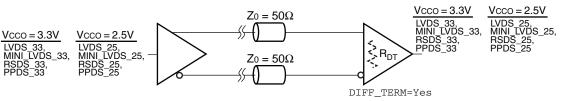

| Differential I/O Standards                                                       |

| On-Chip Differential Termination                                                 |

| DCI Digitally Controlled Impedance                                               |

| Supply Voltages for the IOBs                                                     |

| ESD Protection                                                                   |

| IOBs Organized into Banks                                                        |

| Single-Ended I/O Standard Bank Compatibility                                     |

| Differential I/O Standard Bank Compatibility                                     |

| I/O Banking Rules                                                                |

| Using Large-Swing Signals                                                        |

| I/O and Input-Only Pin Behavior During Power-On, Configuration, and User Mode358 |

| Behavior of Unused I/O Pins After Configuration                                  |

| Related Materials and References                                                 |

| Netaicu Intaictiais allu Netelelilles                                            |

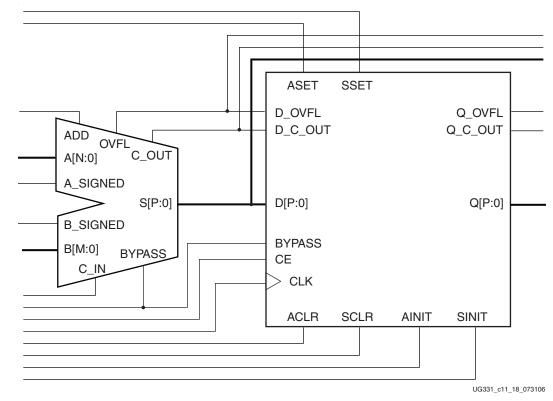

# Chapter 11: Using Embedded Multipliers

| Summary . |  |  |  |  |

|-----------|--|--|--|--|

|-----------|--|--|--|--|

| Introduction                                                                   |

|--------------------------------------------------------------------------------|

| Embedded Multiplier Resource Differences between Spartan-3 Generation Families |

| 362                                                                            |

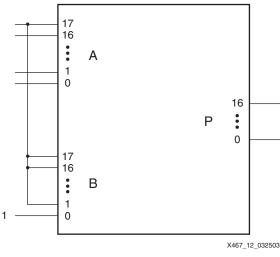

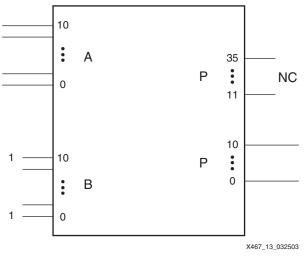

| Two's-Complement Signed Multiplier 362                                         |

| Location Constraints                                                           |

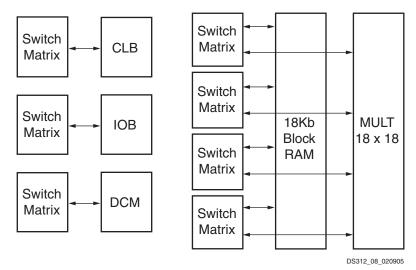

| Multiplier/Block RAM Interaction                                               |

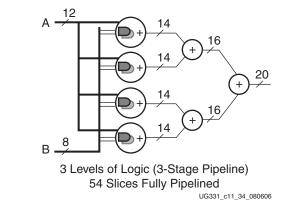

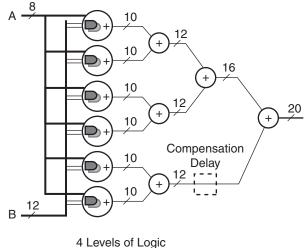

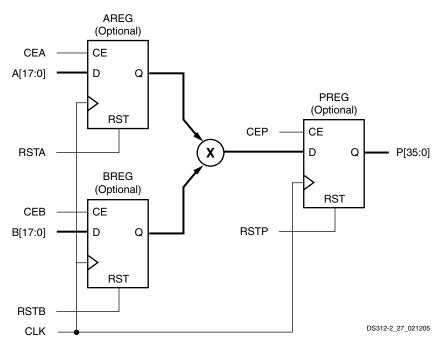

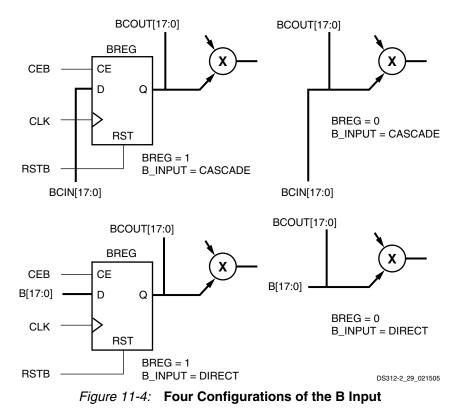

| Optional Pipeline Registers                                                    |

| Timing Specification                                                           |

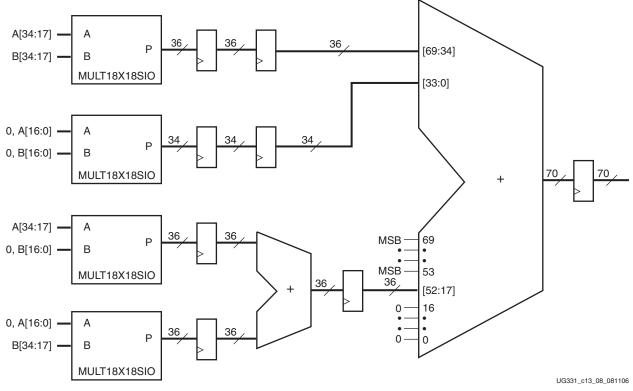

| Expanding Multipliers 366                                                      |

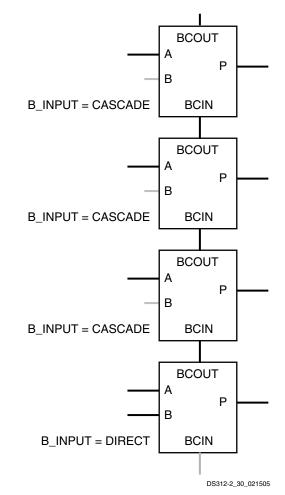

| Cascading Multipliers                                                          |

| Examples                                                                       |

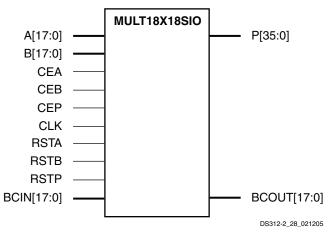

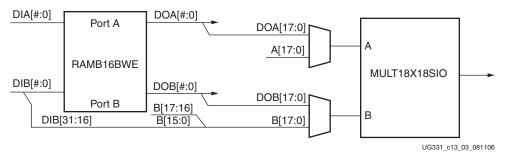

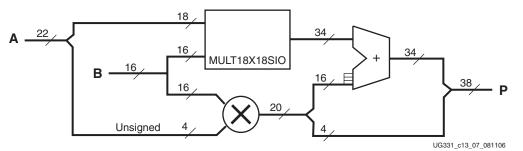

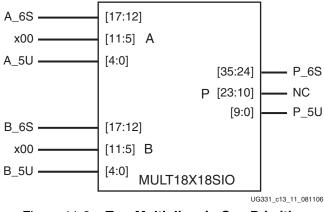

| Two Multipliers in a Single Primitive    369                                   |

| <b>Design Entry</b>                                                            |

| MULT_STYLE Constraint    372                                                   |

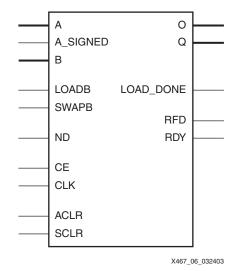

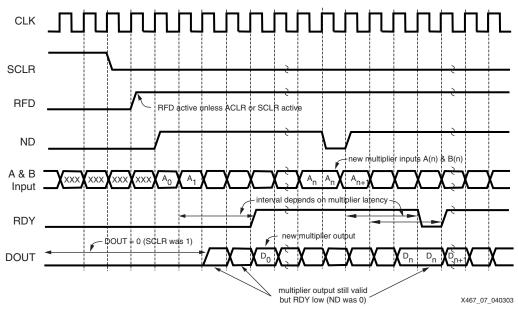

| Using the CORE Generator System                                                |

| System Generator                                                               |

| MAC Cores                                                                      |

| Spartan-3 Family Library Primitives                                            |

| Data Flow                                                                      |

| Multipliers in the Spartan-3 Generation Architecture                           |

| Alternative Applications to Multiplication                                     |

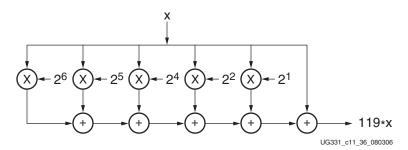

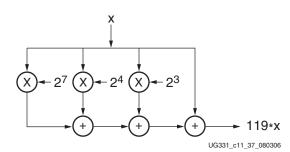

| Shifter                                                                        |

| Magnitude Return                                                               |

| Two's-Complement Return                                                        |

| Complex Multiplication                                                         |

| Time Sharing in Matrix Multiplication                                          |

| Floating-Point Multiplication                                                  |

| Related Materials and References                                               |

| Conclusion                                                                     |

| Appendix A: Two's-Complement Multiplication                                    |

### Chapter 12: Using Interconnect

| <b>Overview</b>                                                | 33 |

|----------------------------------------------------------------|----|

| Interconnect Differences between Spartan-3 Generation Families | 33 |

| Switch Matrix                                                  |    |

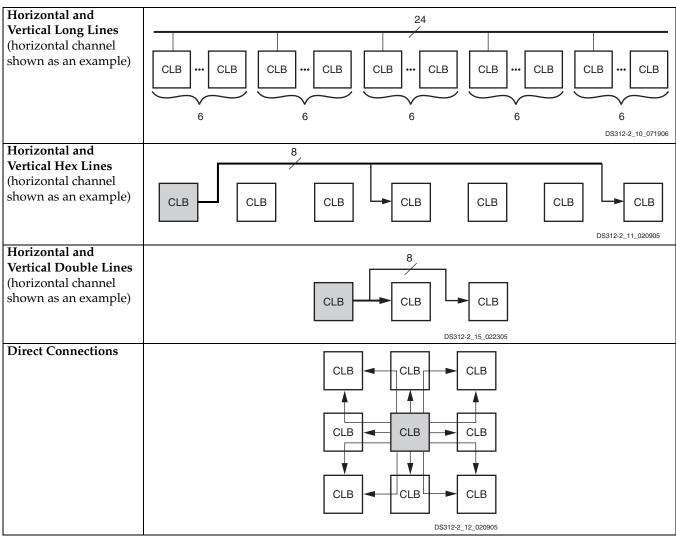

| Long Lines                                                     | 35 |

| Hex Lines                                                      | 35 |

| Double Lines                                                   |    |

| Direct Connections                                             | 36 |

| Viewing Interconnect Details with FPGA Editor                  | 36 |

| Global Controls                                                | 37 |

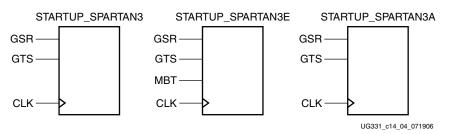

| STARTUP_SPARTAN3 Primitives 38                                 | 37 |

| Summary                                                        | 38 |

### Section II: Design Software

### Chapter 13: Using ISE Design Tools

| Summary                                      | 91  |

|----------------------------------------------|-----|

| Introduction                                 | 91  |

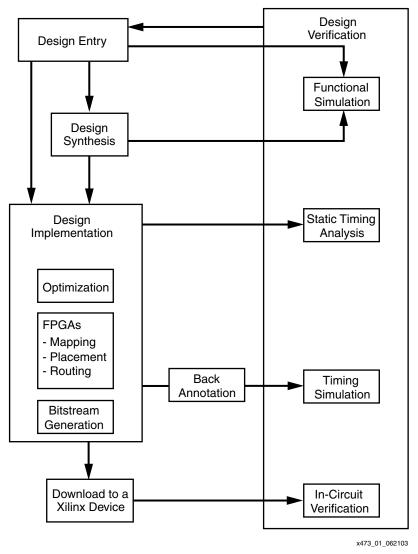

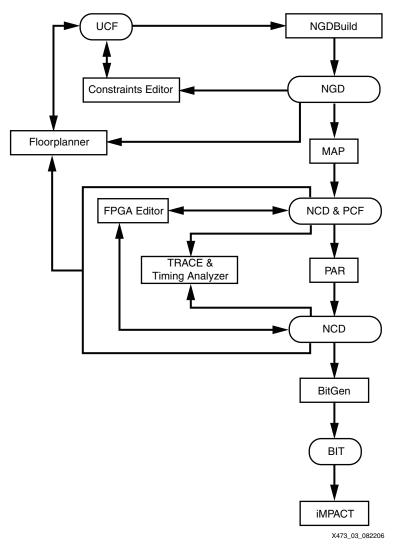

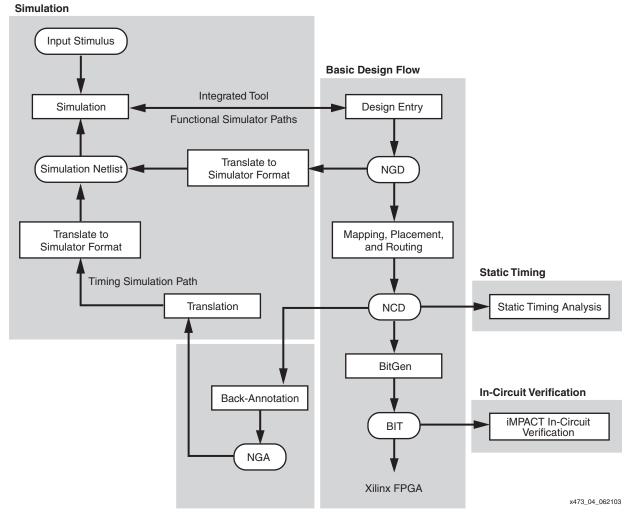

| Design Flow                                  | 91  |

| Design Entry and Synthesis                   |     |

| Hierarchical Design                          |     |

| Schematic Entry                              |     |

| HDL Entry and Synthesis                      |     |

| Constraints                                  |     |

| Design Implementation                        |     |

| Translating                                  |     |

| Mapping                                      |     |

| Placing and Routing                          |     |

| Bitstream Generation                         |     |

| Design Verification                          |     |

| Simulation                                   |     |

| Static Timing Analysis                       |     |

| In-Circuit Verification                      |     |

| ISE Development Environment                  |     |

| Introduction to ISE Tools                    |     |

| Design Entry                                 |     |

| Synthesis                                    |     |

| Simulation                                   |     |

| Implementation                               |     |

| Device Download                              |     |

| ISE Versions                                 |     |

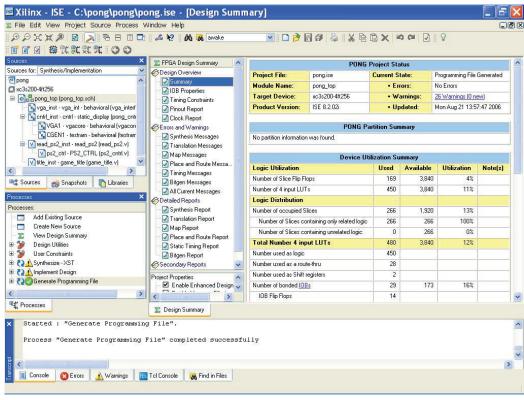

| Project Navigator                            |     |

| Project Navigator Main Window                |     |

| Project                                      |     |

| Sources                                      |     |

| Source Hierarchy                             |     |

| ISE Tools                                    |     |

| Engineering Capture System (ECS)             |     |

| HDL Editor                                   |     |

| StateCAD State Machine Editor                |     |

| Xilinx Synthesis Technology (XST)            |     |

| HDL Advisor                                  |     |

| Partner Tools                                |     |

| Intellectual Property (IP)                   |     |

| CORE Generator System                        |     |

| System Generator for DSP 4                   |     |

| Embedded Development Kit and Platform Studio |     |

| Clocking Wizard. 4                           |     |

| Data2MEM Tool                                | 08  |

| Automatic Implementation Tools               | 08  |

| Incremental Design                           | 08  |

| Modular Design                               |     |

| Constraints Editor                           | .09 |

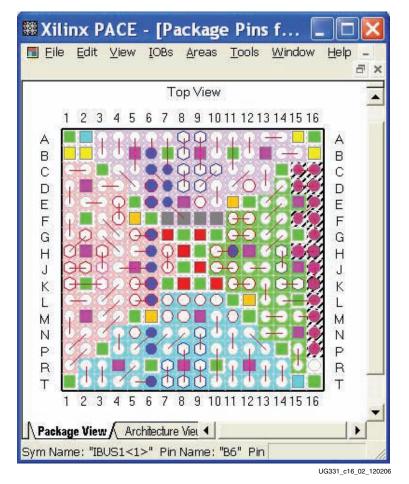

| PACE                                         | .09 |

| Floorplanner                                 | .09 |

| PlanAhead Tool                               | 10  |

| FPGA Editor                                  | 10  |

| HDL Bencher Software             | <br>410 |

|----------------------------------|---------|

| Interactive Timing Analyzer      | <br>411 |

| ISE Simulator                    | <br>411 |

| iMPACT Configuration Tool        | <br>411 |

| ChipScope Pro Analyzer           | <br>411 |

| Power Analysis Tools             | <br>412 |

| Related Materials and References | <br>412 |

| Conclusion                       | <br>412 |

### **Chapter 14: Using IP Cores**

| Summary                                   |

|-------------------------------------------|

| The CORE Generator System                 |

| Xilinx IP Solutions and the IP Center 413 |

| LogiCORE Products                         |

| AllianceCORE Products                     |

| Candidate Core Products 414               |

| Design Files                              |

| Xilinx Alliance Program Partner Services  |

| SignOnce                                  |

| Spartan-3 Generation IP Cores 415         |

| Related Materials and References 433      |

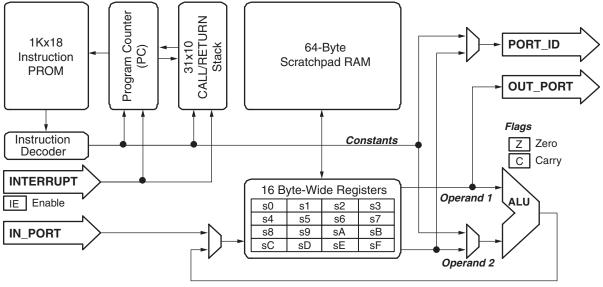

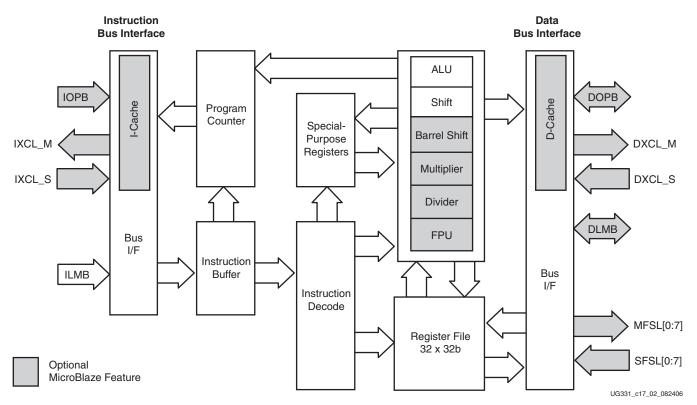

### **Chapter 15: Embedded Processing and Control Solutions**

### Section III: PCB Design Considerations

### **Chapter 16: Packages and Pinouts**

| Summary                                                   | 445 |

|-----------------------------------------------------------|-----|

| Differences in Pinouts Between Spartan-3 Generation FPGAs | 445 |

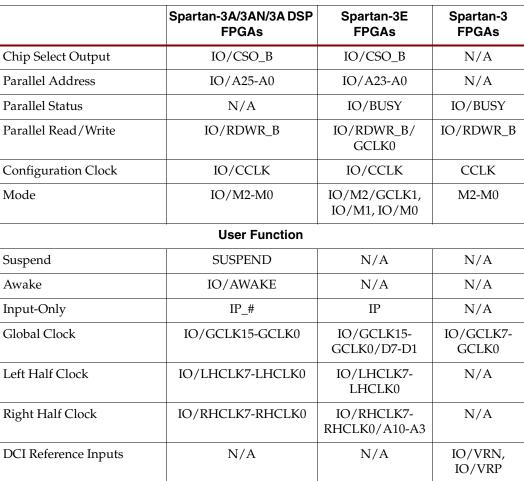

| Pin Types                                                 | 447 |

| Pin Labeling                                              | 448 |

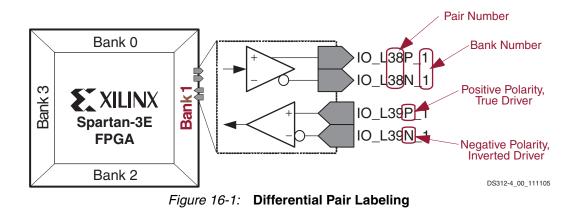

| Differential Pair Labeling 44                                     |

|-------------------------------------------------------------------|

| Pinout Files                                                      |

| Pinout Tables                                                     |

| Footprint Diagrams                                                |

| PartGen                                                           |

| ISE Development System Pin Assignment Reports                     |

| Pinout and Area Constraints Editor (PACE) Tool                    |

| Packages                                                          |

| Pb-Free Packages                                                  |

| Differences in Packages Between Spartan-3 Generation Families 45- |

| Selecting the Right Package Option 45-                            |

| Package Thermal Characteristics 45-                               |

| Related Materials and References                                  |

### Chapter 17: Package Drawings

| Summary                                              |

|------------------------------------------------------|

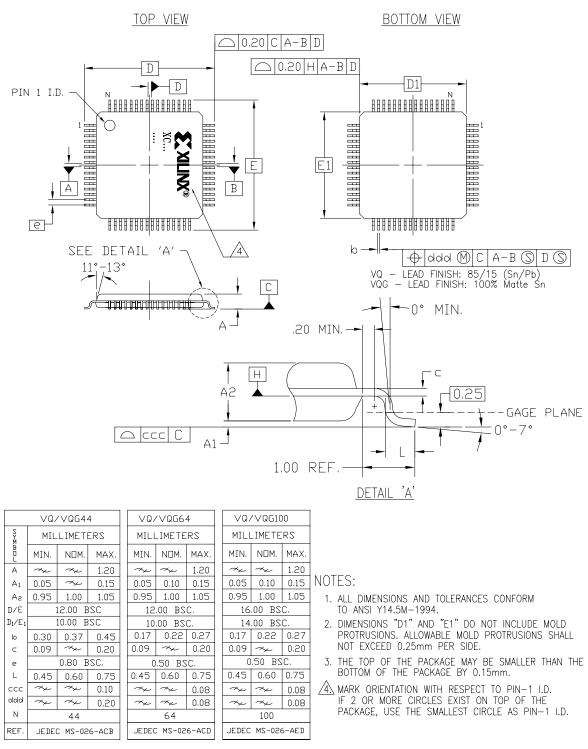

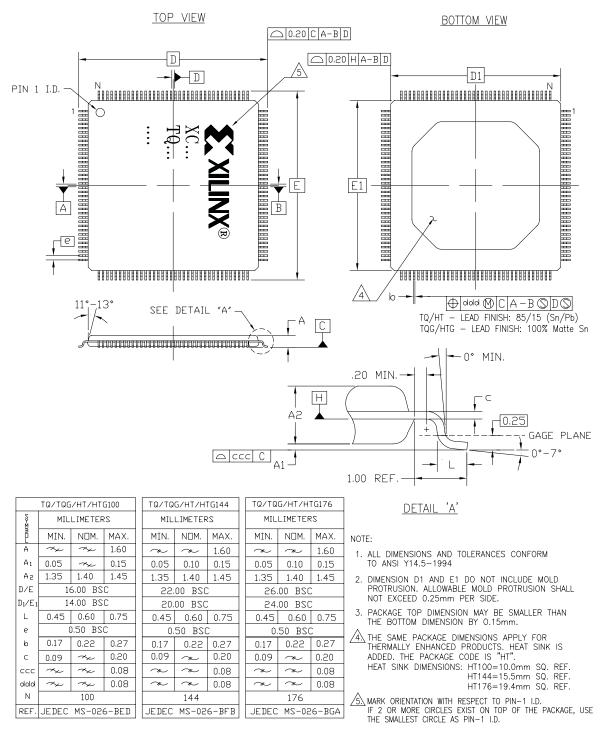

| <b>VQ100/VQG100 Very Thin QFP Package (pk012)</b>    |

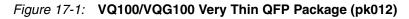

| CP132/CPG132 Chip Scale BGA Package (pk500)459       |

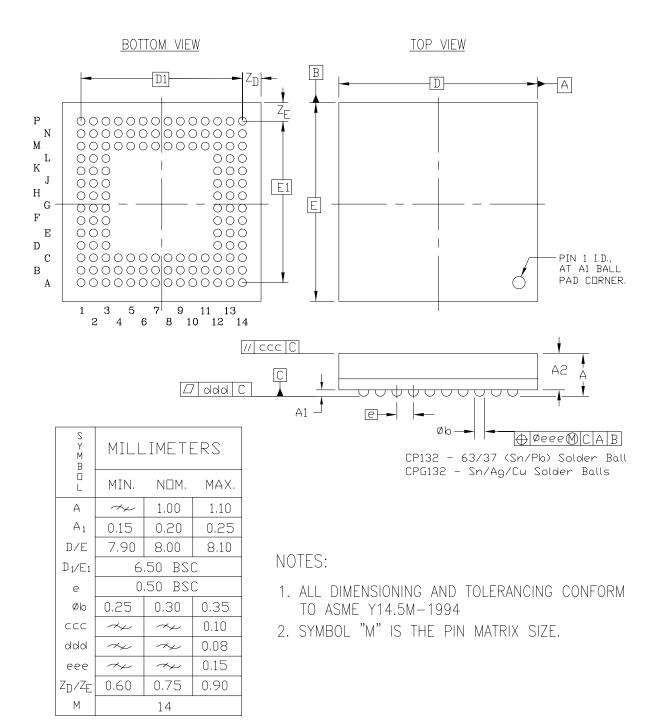

| <b>TQ144/TQG144 Thin QFP Package (pk009)</b> 460     |

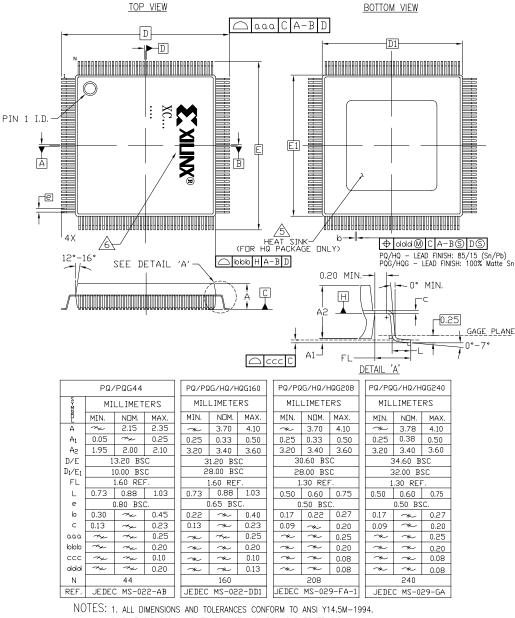

| <b>PQ208/PQG208 QFP Package (pk007)</b>              |

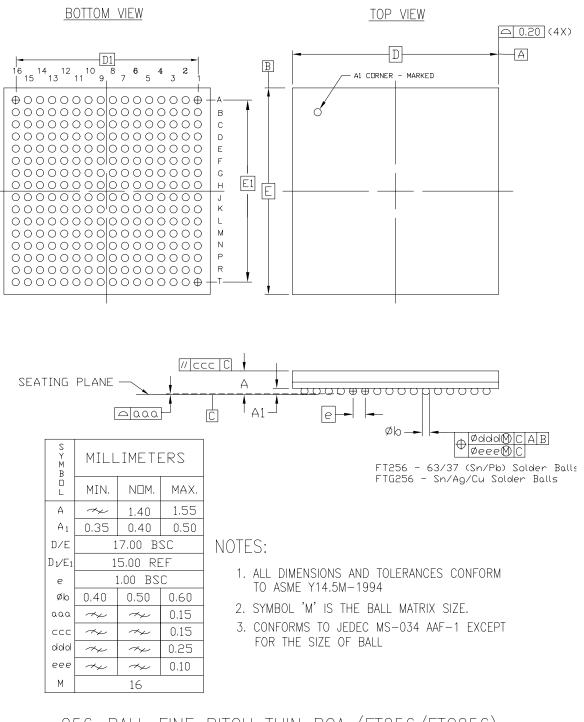

| FT256/FTG256 Fine-Pitch Thin BGA Package (pk053) 462 |

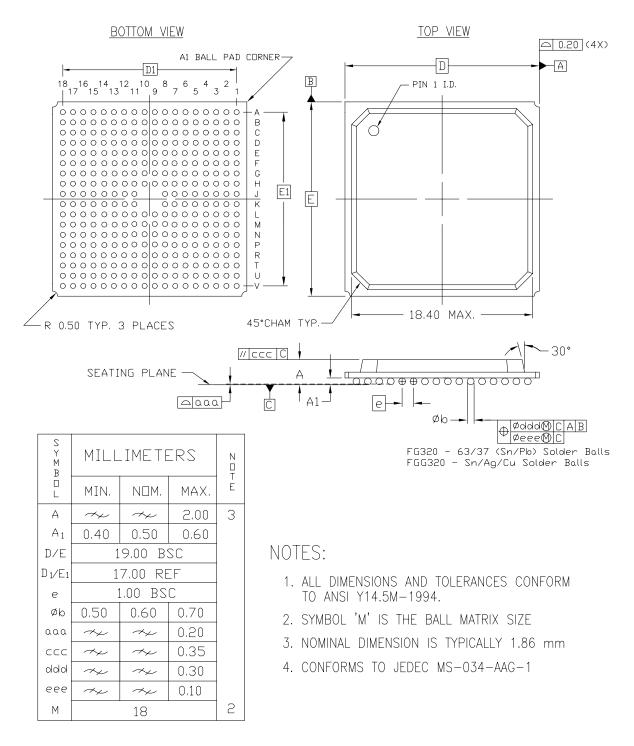

| FG320/FGG320 Fine-Pitch BGA Package (pk071)          |

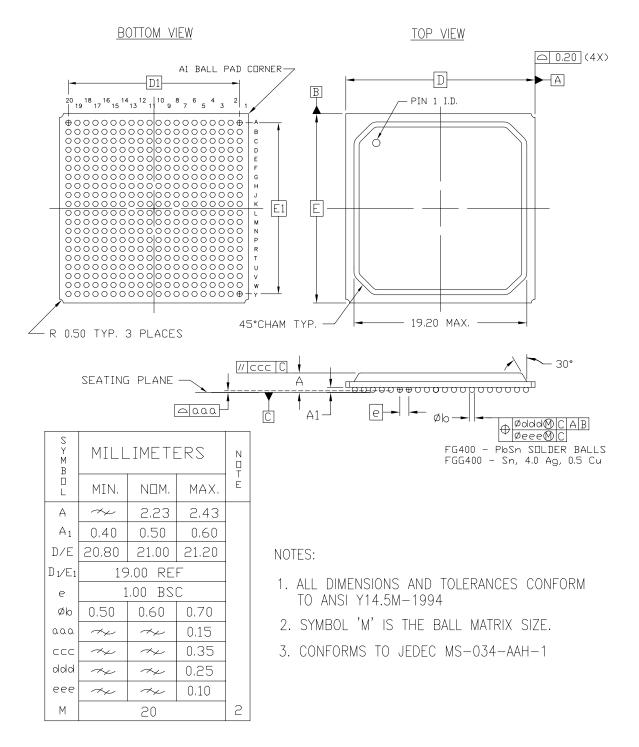

| FG400/FGG400 Fine-Pitch BGA Package (pk083)464       |

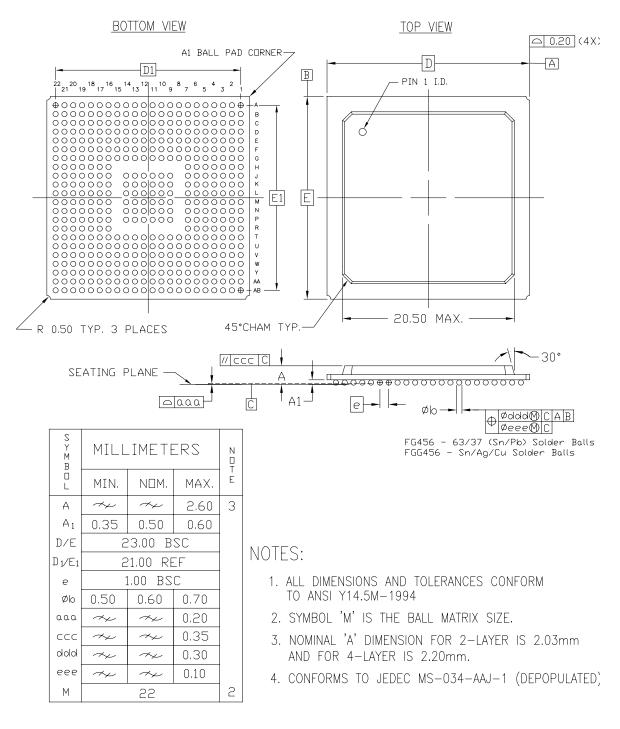

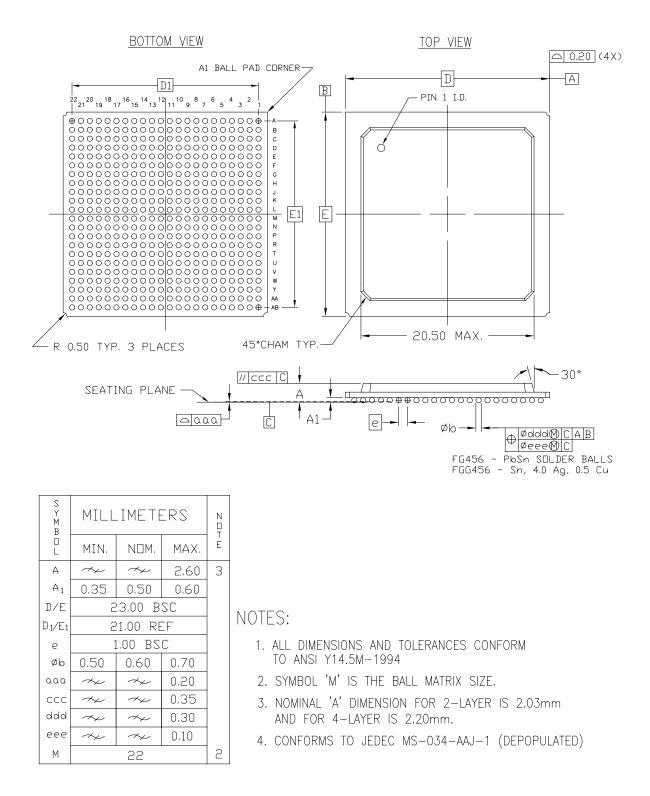

| FG456/FGG456 Fine-Pitch BGA Package (pk034)          |

| FG484/FGG484 Fine-Pitch BGA Package (pk081)466       |

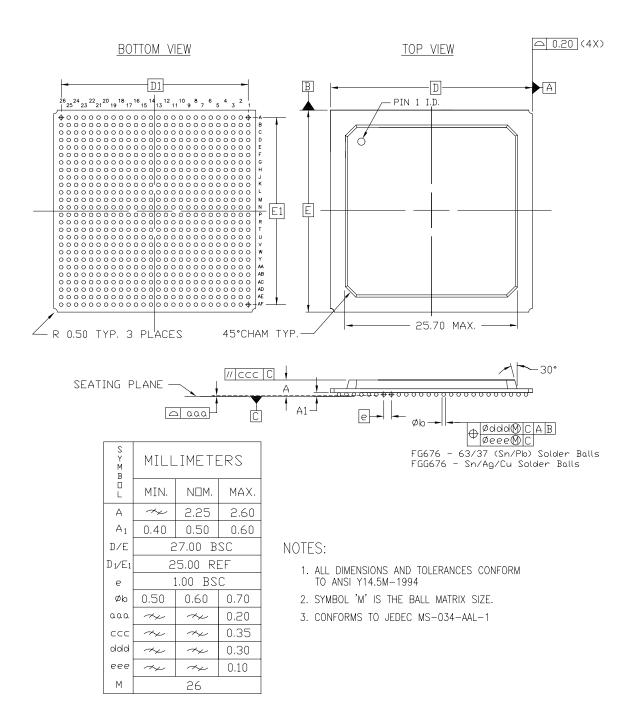

| FG676/FGG676 Fine-Pitch BGA Package (pk035)467       |

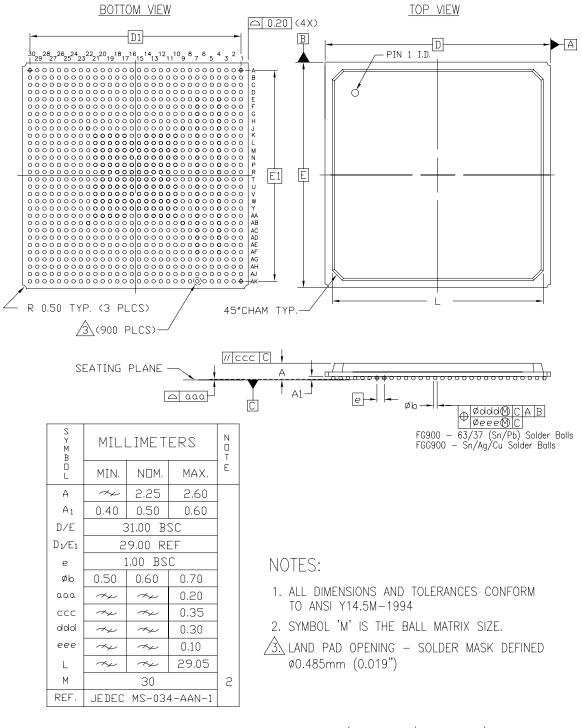

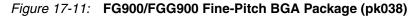

| FG900/FGG900 Fine-Pitch BGA Package (pk038)468       |

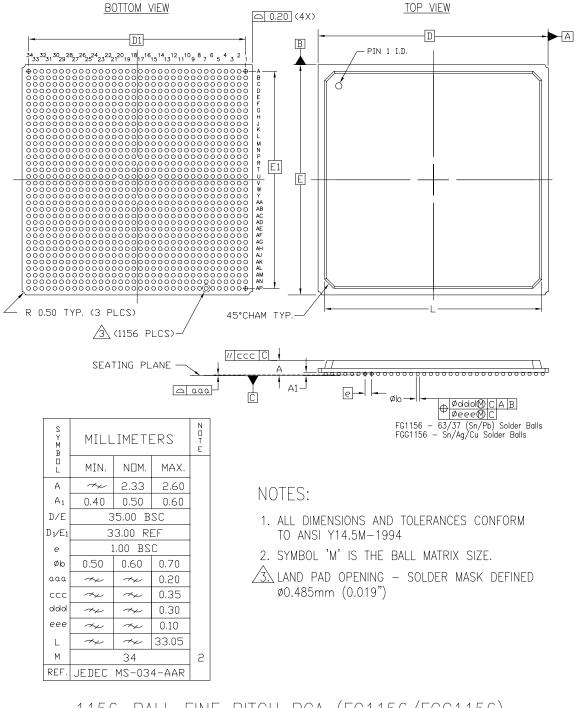

| FG1156/FGG1156 Fine-Pitch BGA Package (pk039) 469    |

### **Chapter 18: Powering Spartan-3 Generation FPGAs**

| Introduction                                                                          |

|---------------------------------------------------------------------------------------|

| Differences between Spartan-3 Generation Families 471                                 |

| Voltage Supplies                                                                      |

| V <sub>REF</sub>                                                                      |

| <b>Power Estimation</b>                                                               |

| Voltage Regulators                                                                    |

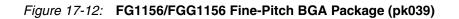

| Power-On Behavior                                                                     |

| Supply Sequencing 474                                                                 |

| Surplus I <sub>CCINT</sub> if V <sub>CCINT</sub> is Applied before V <sub>CCAUX</sub> |

| Ramp Rate                                                                             |

| Hot Swap                                                                              |

| Configuration Data Retention, Brown-Out                                               |

| <b>Saving Power</b>                                                                   |

| Saving Clock Routing Power 476                                                        |

| Power-Off Mode                                                                        |

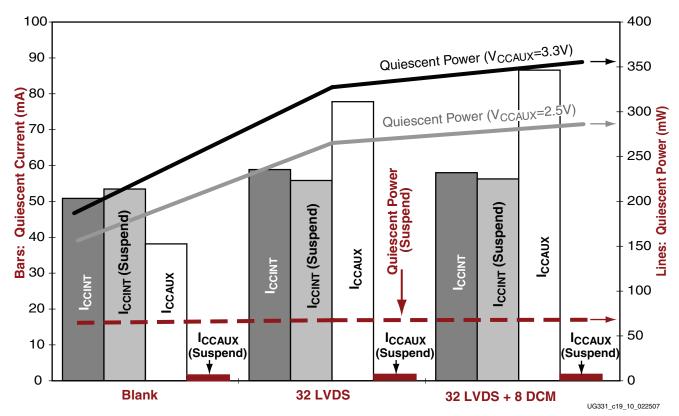

| Suspend Mode                                                                          |

| Board Design and Signal Integrity                                    | 9 |

|----------------------------------------------------------------------|---|

| Simultaneously Switching Outputs                                     |   |

| Power Distribution System Design and Decoupling/Bypass Capacitors 47 | 9 |

| No Internal Charge Pumps or Free-Running Oscillators                 | 0 |

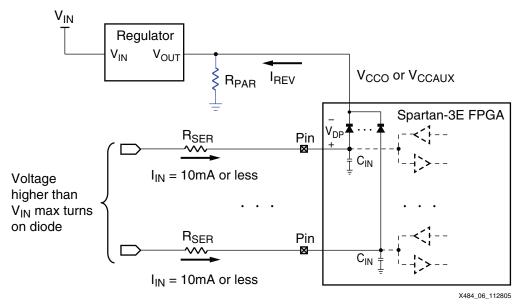

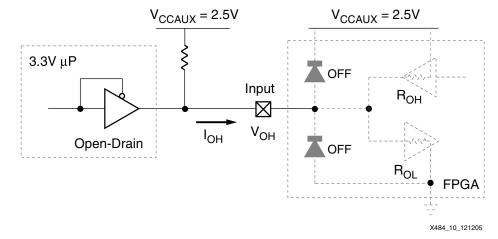

| Large-Swing Signals 48                                               | 0 |

| Related Documents 48                                                 | 0 |

### **Chapter 19: Power Management Solutions**

| Overview                                                                           | 481         |

|------------------------------------------------------------------------------------|-------------|

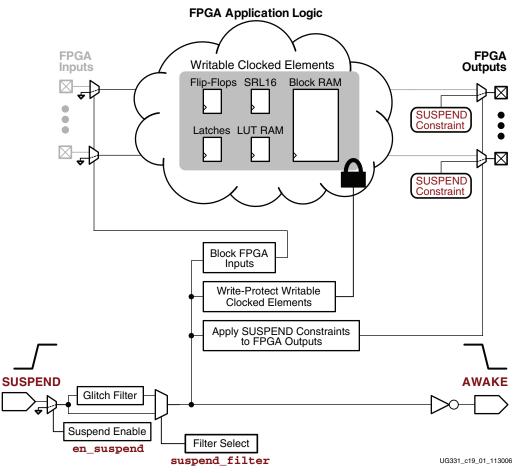

| Spartan-3A/3AN/3A DSP Suspend Mode                                                 | 482         |

| Suspend Features and Benefits                                                      |             |

| Design Preparation for Suspend Mode                                                |             |

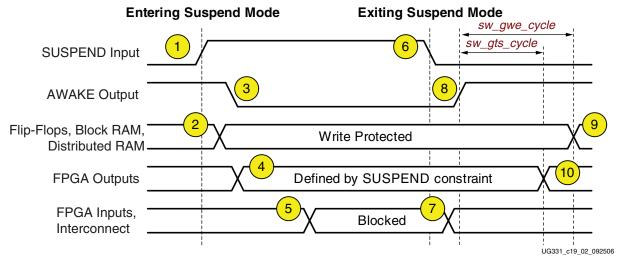

| Entering Suspend Mode                                                              |             |

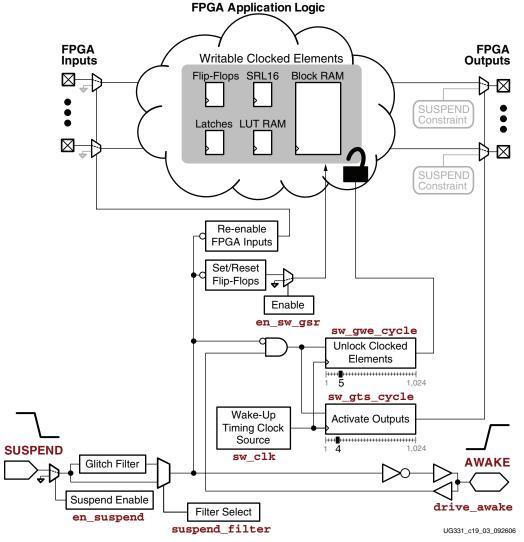

| Exiting Suspend Mode                                                               |             |

| PROG_B Programming Pin Always Overrides Suspend Mode                               | 487         |

| Suspend Mode Timing Example                                                        | 487         |

| Enable the Suspend Feature                                                         | 488         |

| Via User Constraints File (UCF)                                                    | 488         |

| Via BitGen                                                                         |             |

| Define the I/O Behavior During Suspend Mode                                        | 489         |

| Single-Ended I/O Standards                                                         | 489         |

| Differential I/O Standards                                                         | 489         |

| SUSPEND Constraint                                                                 | 490         |

| Application State Retained during Suspend Mode                                     | 490         |

| Suspend Mode Wake-Up Timing Controls                                               | 490         |

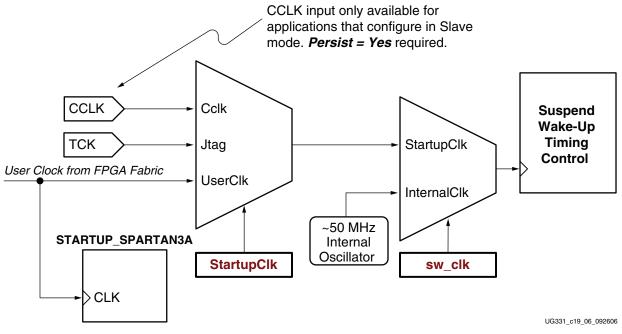

| Wake-Up Timing Clock Source (sw_clk)                                               |             |

| Switch Outputs from Suspend to Normal Behavior (sw_gts_cycle)                      |             |

| Release Write Protect on Clocked Elements (sw_gwe_cycle)                           |             |

| Dedicated Configuration Pins Unaffected During Suspend Mode                        |             |

| SUSPEND Pin                                                                        |             |

| Characteristics                                                                    |             |

| SUSPEND Input Glitch Filter                                                        | 493         |

| Effect on FPGA Configuration                                                       |             |

| Tie SUSPEND to GND if not Using Suspend Mode                                       |             |

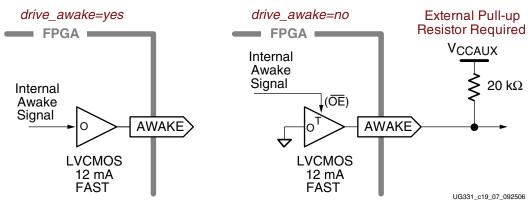

| AWAKE Pin                                                                          |             |

| General Behavior (Suspend Feature Disabled)                                        |             |

| AWAKE Pin Behavior when Suspend Feature Enabled                                    |             |

| Controlling Wake-Up from an External Source                                        |             |

| JTAG Operations Allowed During Suspend Mode                                        |             |

| Post-Configuration CRC Limitations When Using Suspend Mode                         |             |

| Suspend Mode Bitstream Generator Options                                           |             |

| FPGA Voltage Requirements During Suspend Mode                                      |             |

| Supply Requirements During Suspend Mode                                            |             |

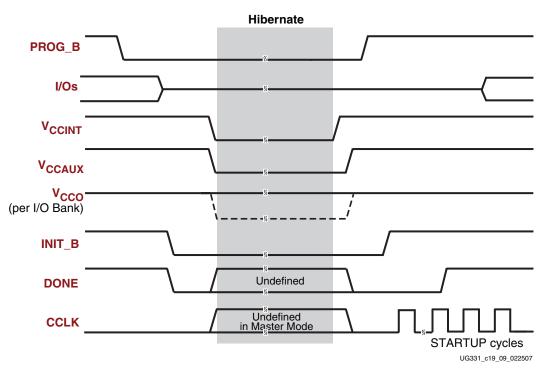

| Hibernate Mode                                                                     | 497         |

| Forcing FPGA to Quiescent Current Levels                                           | 497         |

| Entering Hibernate Mode                                                            | 497         |

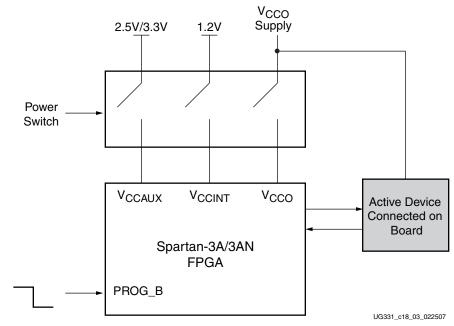

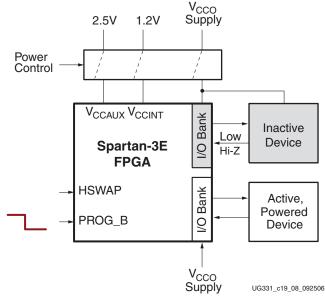

| Spartan-3A/3AN/3A DSP FPGA: Turn Off V <sub>CCO</sub>                              | 498         |

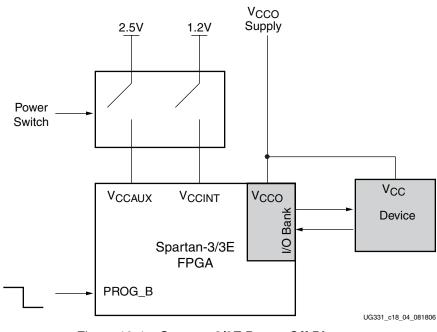

| Spartan-3E and Spartan-3 FPGAs: Maintain $V_{CCO}$ on I/O Banks Connected to Power | ed External |

| Devices                                                                            |             |

| Exiting Hibernate Mode                                                             |             |

| Design Considerations                                                              | 500         |

### Chapter 20: Using IBIS Models

| Summary                    | 501 |

|----------------------------|-----|

| Introduction               | 501 |

| IBIS Advantages over SPICE | 501 |

| IBIS Background            | 502 |

| Xilinx Support of IBIS     | 503 |

| IBIS I/V and dV/dt Curves  | 503 |

| Ramp and dV/dt Curves      | 504 |

| IBISWriter                 | 504 |

| References                 | 504 |

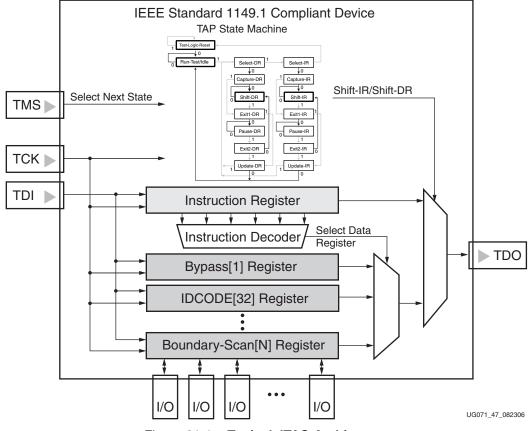

### Chapter 21: Using Boundary-Scan and BSDL Files

| Summary 505                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------|

| Boundary-Scan Overview                                                                                                        |

| IEEE Standards                                                                                                                |

| Boundary-Scan Functions 506                                                                                                   |

| Boundary-Scan Tools                                                                                                           |

| BSDL Files507BSDL File Composition508BSDL File Verification510Using BSDLAnno for Post-Configuration Boundary-Scan Behavior510 |

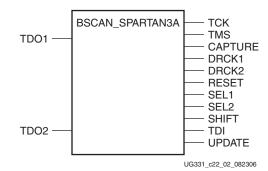

| Software Support511iMPACT511SVF Files511J Drive Engine for IEEE 1532 Programming512Using the BSCAN_SPARTAN3A Macro512         |

| Related Materials and References 513                                                                                          |

# Preface

# About This Guide

This user guide provides guidance on how customers can use the architectural features of each platform in the Spartan<sup>TM</sup>-3 Generation: the Spartan-3, Spartan-3E, Spartan-3A, Spartan-3AN, and Spartan-3A DSP platforms. By combining documentation for these platforms, similarities and differences are easier to learn, and less material needs to be duplicated in multiple sources. These platforms are complementary solutions for new designs. For an overview of how these platforms compare, see "Section I: Designing with Spartan-3 Generation FPGAs" or

http://www.xilinx.com/products/silicon\_solutions/fpgas/spartan\_series/index.htm.

This user guide includes much of the information previously included in Module 2 (Functional Description) of the Spartan data sheets and in device application notes. The data sheets should still be referenced for the platform-specific DC and Switching Characteristics (located in Module 3) and the pinout information (located in Module 4). All features of the Spartan-3E and Spartan-3A/3AN/3A DSP platforms are described in this user guide, but some differences in the Spartan-3 platform, such as DCI or the clocking structure, are discussed in Module 2 of the Spartan-3 data sheet or in the device application notes.

Information on the configuration features of the Spartan-3 Generation FPGAs is located in UG332, the *Spartan-3 Generation Configuration User Guide*. Information on using the internal SPI flash of the Spartan-3AN FPGAs is located in UG333, *Spartan-3AN In-System Flash User Guide*. Together with the device specifications in the data sheets, these user guides provide complete documentation on the Spartan-3 Generation architecture.

Check for updates on xilinx.com at:

http://www.xilinx.com/xlnx/xweb/xil\_publications\_display.jsp?category=User+Guides /FPGA+Device+Families/Spartan-3A. To get an automatic notification of any updates to this document, click the "alert me when page changes" icon on the top of the page.

To provide feedback about this document, click the following link in the electronic version.

Provide Feedback on UG331: Spartan-3 Generation FPGA User Guide <a href="http://www.xilinx.com/xlnx/xweb/xil\_feedback.jsp?key=ug331.pdf&contentType="http://www.xilinx.com/xlnx/xweb/xil\_feedback.jsp?key=ug331.pdf&contentType="http://www.xilinx.com/xlnx/xweb/xil\_feedback.jsp?key=ug331.pdf&contentType="http://www.xilinx.com/xlnx/xweb/xil\_feedback.jsp?key=ug331.pdf&contentType="http://www.xilinx.com/xlnx/xweb/xil\_feedback.jsp?key=ug331.pdf&contentType="http://www.xilinx.com/xlnx/xweb/xil\_feedback.jsp?key=ug331.pdf&contentType="http://www.xilinx.com/xlnx/xweb/xil\_feedback.jsp?key=ug331.pdf&contentType="http://www.xilinx.com/xlnx/xweb/xil\_feedback.jsp?key=ug331.pdf">http://www.xilinx.com/xlnx/xweb/xil\_feedback.jsp?key=ug331.pdf</a>

### **Guide Contents**

This user guide contains the following chapters:

- "Section I: Designing with Spartan-3 Generation FPGAs"

- Chapter 1, "Overview"

- Chapter 2, "Using Global Clock Resources"

- Chapter 3, "Using Digital Clock Managers (DCMs)"

- Chapter 4, "Using Block RAM"

- Chapter 5, "Using Configurable Logic Blocks (CLBs)"

- Chapter 6, "Using Look-Up Tables as Distributed RAM"

- Chapter 7, "Using Look-Up Tables as Shift Registers (SRL16)"

- Chapter 8, "Using Dedicated Multiplexers"

- Chapter 9, "Using Carry and Arithmetic Logic"

- Chapter 10, "Using I/O Resources"

- Chapter 11, "Using Embedded Multipliers"

- Chapter 12, "Using Interconnect"

- "Section II: Design Software"

- Chapter 13, "Using ISE Design Tools"

- Chapter 14, "Using IP Cores"

- Chapter 15, "Embedded Processing and Control Solutions"

- "Section III: PCB Design Considerations"

- Chapter 16, "Packages and Pinouts"

- Chapter 17, "Package Drawings"

- Chapter 18, "Powering Spartan-3 Generation FPGAs"

- Chapter 19, "Power Management Solutions"

- Chapter 20, "Using IBIS Models"

- Chapter 21, "Using Boundary-Scan and BSDL Files"

### **Additional Resources**

To find additional documentation, see the Xilinx website at:

http://www.xilinx.com/literature.

To search the Answer Database of silicon, software, and IP questions and answers, or to create a technical support WebCase, see the Xilinx website at:

http://www.xilinx.com/support.

### Conventions

This document uses the following conventions. An example illustrates each convention.

### Typographical

The following typographical conventions are used in this document:

| Convention   | Meaning or Use                                                      | Example              |

|--------------|---------------------------------------------------------------------|----------------------|

| Courier font | Messages, prompts, and<br>program files that the system<br>displays | speed grade: - 100   |

| Courier bold | Literal commands that you enter in a syntactical statement          | ngdbuild design_name |

| Convention                  | Meaning or Use                                                                                                        | Example                                                                                                  |  |  |  |  |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--|--|--|--|

| Helvetica bold              | Commands that you select from a menu                                                                                  | File <i>→</i> Open                                                                                       |  |  |  |  |

|                             | Keyboard shortcuts                                                                                                    | Ctrl+C                                                                                                   |  |  |  |  |

|                             | Variables in a syntax statement<br>for which you must supply<br>values                                                | ngdbuild design_name                                                                                     |  |  |  |  |

| Italic font                 | References to other manuals                                                                                           | See the <i>Development System</i><br><i>Reference Guide</i> for more<br>information.                     |  |  |  |  |

|                             | Emphasis in text                                                                                                      | If a wire is drawn so that it<br>overlaps the pin of a symbol, the<br>two nets are <i>not</i> connected. |  |  |  |  |

| Square brackets []          | An optional entry or parameter.<br>However, in bus specifications,<br>such as <b>bus[7:0]</b> , they are<br>required. | <b>ngdbuild</b> [option_name]<br>design_name                                                             |  |  |  |  |

| Braces { }                  | A list of items from which you must choose one or more                                                                | lowpwr ={on off}                                                                                         |  |  |  |  |

| Vertical bar                | Separates items in a list of choices                                                                                  | lowpwr ={on off}                                                                                         |  |  |  |  |

| Vertical ellipsis<br>•<br>• | Repetitive material that has been omitted                                                                             | IOB #1: Name = QOUT'<br>IOB #2: Name = CLKIN'                                                            |  |  |  |  |

| Horizontal ellipsis         | Repetitive material that has been omitted                                                                             | <b>allow block</b> block_name loc1 loc2 locn;                                                            |  |  |  |  |

### **Online Document**

The following conventions are used in this document:

| Convention            | Meaning or Use                                             | Example                                                                                                         |  |  |  |

|-----------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|

| Blue text             | Cross-reference link to a location in the current document | See the section "Additional<br>Resources" for details.<br>Refer to "Title Formats" in<br>Chapter 1 for details. |  |  |  |

| Blue, underlined text | Hyperlink to a website (URL)                               | Go to <u>http://www.xilinx.com</u><br>for the latest speed files.                                               |  |  |  |

www.xilinx.com

24

# Section I: Designing with Spartan-3 Generation FPGAs

"Overview"

"Using Global Clock Resources"

"Using Digital Clock Managers (DCMs)"

"Using Block RAM"

"Using Configurable Logic Blocks (CLBs)"

"Using Look-Up Tables as Distributed RAM"

"Using Look-Up Tables as Shift Registers (SRL16)"

"Using Dedicated Multiplexers"

"Using Carry and Arithmetic Logic"

"Using I/O Resources"

"Using Embedded Multipliers"

"Using Interconnect"

26

# Chapter 1

# Overview

This chapter provides an overview of the Spartan<sup>™</sup>-3 Generation platforms. Refer to the links in Table 1-1 for more information.

Table 1-1: Spartan-3 Generation Platforms

| Platform             | Product Information                | Technical Documentation                                                                                                    |

|----------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Spartan-3A DSP FPGAs | http://www.xilinx.com/spartan3adsp | http://www.xilinx.com/xlnx/xweb/xil_publications_display.jsp?<br>category=Publications/FPGA+Device+Families/Spartan-3A+DSP |

| Spartan-3AN FPGAs    | http://www.xilinx.com/spartan3an   | http://www.xilinx.com/xlnx/xweb/xil_publications_display.jsp?<br>category=Publications/FPGA+Device+Families/Spartan-3AN    |

| Spartan-3A FPGAs     | http://www.xilinx.com/spartan3a    | http://www.xilinx.com/xlnx/xweb/xil_publications_display.jsp?<br>category=Publications/FPGA+Device+Families/Spartan-3A     |

| Spartan-3E FPGAs     | http://www.xilinx.com/spartan3e    | http://www.xilinx.com/xlnx/xweb/xil_publications_display.jsp?<br>category=Publications/FPGA+Device+Families/Spartan-3E     |

| Spartan-3 FPGAs      | http://www.xilinx.com/spartan3     | http://www.xilinx.com/xlnx/xweb/xil_publications_display.jsp?<br>category=Publications/FPGA+Device+Families/Spartan-3      |

### Introduction

The Spartan-3 Generation of FPGAs includes the popular, high-volume Spartan-3, Spartan-3E, Spartan-3A, Spartan-3AN, and Spartan-3A DSP platforms. These families of Field Programmable Gate Arrays (FPGAs) are specifically designed to meet the needs of high volume, cost-sensitive electronic applications, such as consumer products. The Spartan-3 Generation includes 25 devices offering densities ranging from 50,000 to 5 million system gates, as shown in Table 1-5 through Table 1-7.